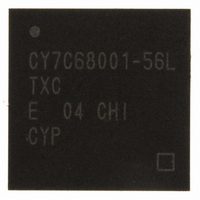

CY7C68001-56LTXC Cypress Semiconductor Corp, CY7C68001-56LTXC Datasheet - Page 50

CY7C68001-56LTXC

Manufacturer Part Number

CY7C68001-56LTXC

Description

IC USB EZ-USB SX2 HS 56VQFN

Manufacturer

Cypress Semiconductor Corp

Series

CY7Cr

Type

USBr

Specifications of CY7C68001-56LTXC

Protocol

USB 2.0

Voltage - Supply

3 V ~ 3.6 V

Mounting Type

Surface Mount

Package / Case

56-VQFN Exposed Pad, 56-HVQFN, 56-SQFN, 56-DHVQFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Drivers/receivers

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

428-2932

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

CY7C68001-56LTXC

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

17.0

Document #: 38-08013 Rev. *B

Description Title: CY7C68001 EZ-USB SX2™ High-Speed USB Interface Device

Document Number: 38-08013

REV.

*A

*B

**

Document Revision History

ECN No. Issue Date

123155

126324

111807

06/07/02

02/07/03

07/02/03

Change

Orig. of

MON

BHA

BHA

New Data Sheet

Minor clean-up and clarification

Removed references to IRQ Register and replaced them with references to

Interrupt Status Byte

Modified pin-out description for XTALIN and XTALOUT

Added CS# timing to Figure 11-10, Figure 11-8, and Figure 11-12

Changed Command Protocol example to IFCONFIG (0x01)

Edited PCB Layout Recommendations

Added AR#10691

Added USB high-speed logo

Default state of registers specified in section where the register bits are defined

Reorganized timing diagram presentation: First all timing related to synchronous

interface, followed by timing related to asynchronous interface, followed by timing

diagrams common to both interfaces

Provided further information in section 3.3 regarding boot methods

Provided timing diagram that encapsulates ALL relevant signals for a synchronous

and asynchronous slave read and write interface

Added section on (QFN) Package Design Notes

FIFOADR[2:0] Hold Time (t

as follows: SLRD/PKTEND to FIFOADR[2:0] Hold Time: 20 ns; SLWR to

FIFOADR[2:0] Hold Time:70 ns (recommended)

Added information on the polarity of the programmable flag

Fixed the Command Synchronous Write Timing Diagram

Fixed the Command Asynchronous Write Timing Diagram

Added information on the delay required when endpoint configuration registers are

changed after SX2 has already enumerated

FAH)

Description of Change

for Asynchronous FIFO Interface has been updated

CY7C68001

Page 50 of 50