EP3C25F324I7 Altera, EP3C25F324I7 Datasheet - Page 93

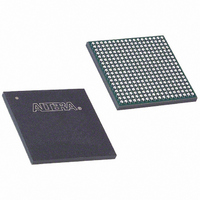

EP3C25F324I7

Manufacturer Part Number

EP3C25F324I7

Description

IC CYCLONE III FPGA 25K 324 FBGA

Manufacturer

Altera

Series

Cyclone® IIIr

Datasheets

1.EP3C5F256C8N.pdf

(5 pages)

2.EP3C5F256C8N.pdf

(34 pages)

3.EP3C5F256C8N.pdf

(66 pages)

4.EP3C5F256C8N.pdf

(14 pages)

5.EP3C5F256C8N.pdf

(76 pages)

6.EP3C25F324I7.pdf

(274 pages)

Specifications of EP3C25F324I7

Number Of Logic Elements/cells

24624

Number Of Labs/clbs

1539

Total Ram Bits

608256

Number Of I /o

215

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

324-FBGA

Family Name

Cyclone III

Number Of Logic Blocks/elements

24624

# I/os (max)

215

Frequency (max)

437.5MHz

Process Technology

65nm

Operating Supply Voltage (typ)

1.2V

Logic Cells

24624

Ram Bits

608256

Operating Supply Voltage (min)

1.15V

Operating Supply Voltage (max)

1.25V

Operating Temp Range

-40C to 100C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

324

Package Type

FBGA

For Use With

544-2370 - KIT STARTER CYCLONE III EP3C25

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Not Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP3C25F324I7N

Manufacturer:

ALTERA32

Quantity:

181

Chapter 5: Clock Networks and PLLs in the Cyclone III Device Family

PLL Reconfiguration

© December 2009

Altera Corporation

Charge Pump and Loop Filter

You can reconfigure the charge pump and loop filter settings to update the PLL

bandwidth in real time.

charge pump (ICP), loop filter resistor (R), and capacitor (C) values for Cyclone III

device family PLLs.

Table 5–5. Charge Pump Bit Control

Table 5–6. Loop Filter Resistor Value Control

Table 5–7. Loop Filter Control of High Frequency Capacitor

Bypassing PLL Counter

Bypassing a PLL counter results in a multiply (M counter) or a divide (N, C0 to C4

counters) factor of one.

LFR[4]

0

0

0

0

1

1

1

1

1

1

1

CP[2]

0

1

1

1

LFC[1]

0

0

1

LFR[3]

0

0

0

1

0

0

0

1

1

1

1

Table 5–5

CP[1]

0

0

1

1

LFR[2]

through

0

0

1

0

0

0

1

0

0

1

1

LFC[0]

0

1

1

Table 5–7

LFR[1]

0

1

0

0

0

1

0

0

1

0

1

CP[0]

list the possible settings for

0

0

0

1

Cyclone III Device Handbook, Volume 1

LFR[0]

0

1

0

0

0

1

0

0

1

0

0

Setting (Decimal)

Setting (Decimal)

0

1

3

(Decimal)

0

1

3

7

Setting

16

19

20

24

27

28

30

0

3

4

8

5–29