IPR-FIR Altera, IPR-FIR Datasheet - Page 44

IPR-FIR

Manufacturer Part Number

IPR-FIR

Description

IP CORE Renewal Of IP-FIR

Manufacturer

Altera

Type

MegaCorer

Specifications of IPR-FIR

Software Application

IP CORE, DSP Filters And Transforms

Supported Families

Arria GX, Arria II GX, Cyclone, HardCopy, Stratix

Core Architecture

FPGA

Core Sub-architecture

Arria, Cyclone, Stratix

Rohs Compliant

NA

Function

Finite Impulse Response Compiler

License

Renewal License

Lead Free Status / RoHS Status

na

Lead Free Status / RoHS Status

na

4–2

FIR Compiler User Guide

■

■

■

■

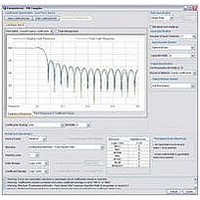

You can adjust the number of taps, cut-off frequencies, sample rate, filter type, and

window method to build a custom frequency response. Each time you apply the

settings, the FIR Compiler calculates the coefficient values and displays the frequency

response on a logarithmic scale. The coefficients are floating-point numbers and must

be scaled.

The values are displayed in the Coefficients scroll-box, of the Coefficients Generator

Dialog box, refer to

When the FIR Compiler reads in the coefficients, it automatically detects any

symmetry. The filter gives you several scaling options, for example, scaling to a

specified number of bits or scaling by a user-specified factor.

The scaled coefficients are displayed in the Time Response & Coefficient Values tab

of the Parameterize FIR Compiler page, refer to

Coefficient Scaling

Coefficient values are often represented as floating-point numbers. To convert these

numbers to a fixed-point system, the coefficients must be multiplied by a scaling

factor and rounded. The FIR Compiler provides five scaling options:

■

■

■

■

■

Band Reject

Raised Cosine

Root Raised Cosine

Half Band (low pass)

Auto scale to a specified number of precision bits—Because the coefficients are

represented by a certain number of bits, it is possible to apply whatever gain factor

is required such that the maximum coefficient value equals the maximum possible

value for a given number of bits. This approach produces coefficient values with

the maximum signal-to-noise ratio.

Auto with a power of 2—With this approach, the FIR Compiler selects the largest

power of two scaling factor that can represent the largest number within a

particular number of bits of resolution. Multiplying all of the coefficients by a

particular gain factor is the same as adding a gain factor before the FIR filter. In

this case, applying a power of two scaling factor makes it relatively easy to remove

the gain factor by shifting a binary decimal point.

Manual—The FIR Compiler lets you manually scale the coefficient values by a

specified gain factor.

Signed binary fractional—You can specify how many digits to use on either side of

the decimal point (supported in the variable architecture only).

None—The FIR Compiler can read in pre-scaled integer values for the coefficients

and not apply scaling factors.

Figure 3–2 on page

3–3.

Figure 3–5 on page

© December 2010 Altera Corporation

Chapter 4: Functional Description

3–6.

FIR Compiler