IPR-FIR Altera, IPR-FIR Datasheet

IPR-FIR

Specifications of IPR-FIR

Related parts for IPR-FIR

IPR-FIR Summary of contents

Page 1

... Innovation Drive San Jose, CA 95134 www.altera.com FIR Compiler User Guide Software Version: 10.1 Document Date: December 2010 ...

Page 2

... Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation ...

Page 3

... Symmetrical Serial . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–3 Coefficient Reloading and Reordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–4 Structure Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–6 Multicycle Variable Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–6 Parallel Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–6 Serial Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–7 Multibit Serial Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–7 Multichannel Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–8 Interpolation and Decimation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4–8 © December 2010 Altera Corporation Contents FIR Compiler User Guide ...

Page 4

... Appendix A. FIR Compiler Supported Device Structures Supported Device Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–1 HardCopy II Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–3 Compiling HardCopy II Designs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A–3 Additional Information Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–1 How to Contact Altera . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–2 Typographic Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info–2 FIR Compiler User Guide Contents © December 2010 Altera Corporation ...

Page 5

... Errata. Altera verifies that the current version of the Quartus previous version of each MegaCore and Errata report any exceptions to this verification. Altera does not verify compilation with MegaCore function versions older than one release. Device Family Support Table 1–2 defines the device support levels for Altera IP cores. ...

Page 6

... Table 1–3 shows the level of support offered by the FIR Compiler to each Altera device family. Table 1–3. Device Family Support Arria GX ™ Arria II GX Arria II GZ Cyclone ® Cyclone II Cyclone III Cyclone III LS Cyclone IV HardCopy II ® HardCopy III HardCopy IV E HardCopy IV GX Stratix ® ...

Page 7

... DSP Builder ready. General Description The Altera FIR Compiler provides a fully integrated finite impulse response (FIR) filter development environment optimized for use with Altera FPGA devices. You can use the IP Toolbench interface to implement a variety of filter architectures, including fully parallel, serial, or multibit serial distributed arithmetic, and multicycle fixed/variable filters ...

Page 8

... Traditionally, designers have been forced to make a trade-off between the flexibility of digital signal processors and the performance of ASICs and application-specific standard product (ASSPs) digital signal processing (DSP) solutions. The Altera DSP solution reduces the need for this trade-off by providing exceptional performance combined with the flexibility of FPGAs. ...

Page 9

... Chapter 1: About This Compiler General Description Figure 1–3 shows a typical DSP system that uses Altera MegaCore functions. Figure 1–3. Typical Modulator System Outer Encoding Layer FEC Convolutional Input Reed Solomon Interleaver Data Encoder DSP processors have a limited number of multiply accumulators (MACs), and require many clock cycles to compute each output value (the number of cycles is directly related to the order of the filter) ...

Page 10

... MegaCore Verification Before releasing an updated version of the FIR Compiler, Altera runs a comprehensive regression test to verify its quality and correctness. All features and architectures are tested by sweeping all parameter options and verifying that the simulation matches a master functional model. Performance and Resource Utilization This section shows typical expected performance for a FIR Compiler MegaCore function with Cyclone III and Stratix IV devices ...

Page 11

... Notes to Table 1–6: (1) GMAC = giga multiply accumulates per second (1 giga = 1,000 million). (2) This FIR filter takes advantage of symmetric coefficients. (3) Using EP4SGX70DF29C2X devices. (4) The data width is 16-bits and there are 4 serial units. © December 2010 Altera Corporation Memory (6) Multipliers M9K (9x9) 3 — ...

Page 12

... After you purchase a license, you can request a license file from the Altera website at www.altera.com/licensing and install it on your computer. When you request a license file, Altera emails you a license.dat file. If you do not have Internet access, contact your local Altera representative ...

Page 13

... The untethered timeout for the FIR Compiler MegaCore function is one hour; the tethered timeout value is indefinite. The data output signal is forced to zero when the hardware evaluation time expires. © December 2010 Altera Corporation Megafunctions. FIR Compiler User Guide 1–9 ...

Page 14

... FIR Compiler User Guide Chapter 1: About This Compiler Installation and Licensing © December 2010 Altera Corporation ...

Page 15

... In DSP Builder, a Simulink symbol for the FIR Compiler appears in the MegaCore Functions library of the Altera DSP Builder Blockset in the Simulink library browser. You can use the FIR Compiler in the MATLAB/Simulink environment by performing the following steps: 1 ...

Page 16

... Click Next and select FIR Compiler <version> from the DSP>Filters section in the Installed Plug-Ins tab. FIR Compiler User Guide DSP Builder User Guide. (Figure (Figure 2–2). © December 2010 Altera Corporation Chapter 2: Getting Started MegaWizard Plug-In Manager Flow Memory-Mapped ® Avalon Interface 2–1). ...

Page 17

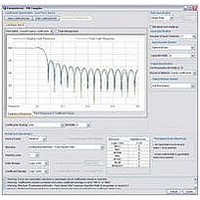

... Click Step 1: Parameterize in IP Toolbench to display the Parameterize - FIR Compiler window. Use this interface to specify the required parameters for the MegaCore function variation. For an example of how to set parameters for the FIR Compiler MegaCore function, refer to © December 2010 Altera Corporation (Figure 2–3 on page 2–4). Chapter 3, Parameter Settings ...

Page 18

... Figure 2–4. Set Up Simulation 3. Turn on Generate Simulation Model to create an IP functional model functional simulation model is a cycle-accurate VHDL or Verilog HDL model produced by the Quartus II software. FIR Compiler User Guide (Figure 2–4). Chapter 2: Getting Started MegaWizard Plug-In Manager Flow © December 2010 Altera Corporation ...

Page 19

... FIR Compiler design in the MATLAB environment. A testbench is also generated. Figure 2–5. Create a MATLAB M-File 7. Click Finish. 1 The Quartus II Testbench tab contains an option that is not used in this version of the FIR Compiler and should be ignored. © December 2010 Altera Corporation 2–5 (Figure 2–5). FIR Compiler User Guide ...

Page 20

... A single Quartus II IP file is generated that contains all of the assignments and other information required to process your MegaCore function variation in the Quartus II compiler. You are prompted to add this file to the current Quartus II project when you exit from IP Toolbench. Chapter 2: Getting Started MegaWizard Plug-In Manager Flow © December 2010 Altera Corporation ...

Page 21

... The <entity name> prefix is added automatically. The VHDL code for each MegaCore instance is generated dynamically when you click Finish so that the <entity name> is different for every instance generated from the <variation name> by appending _ast. © December 2010 Altera Corporation (Note 1) ,(2) Description Quartus II vector file ...

Page 22

... The output from the simulation is stored in a file <variation name>_output.txt. FIR Compiler User Guide (Figure 2–7). For a full description of the signals supported page chapter in volume 3 of the Quartus II Handbook. Chapter 2: Getting Started MegaWizard Plug-In Manager Flow Table 4–3 on 2–3. Simulating © December 2010 Altera Corporation ...

Page 23

... On the Tools menu, point to EDA Simulation Tool and click Run EDA RTL Simulation. The Quartus II software selects the simulator, and compiles the Altera libraries, design files, and testbenches. The testbench runs and the waveform window shows the design signals for analysis. ...

Page 24

... FIR Compiler User Guide Chapter 2: Getting Started MegaWizard Plug-In Manager Flow © December 2010 Altera Corporation ...

Page 25

... You can click New Coefficient Set on this page to define or load new coefficients. Alternatively, or you can click Edit Coefficient Set to edit the default coefficient set or Remove Coefficient Set to clear the currently loaded coefficients. © December 2010 Altera Corporation 3. Parameter Settings 3–2. 3–6.) shows the Parameterize - FIR Compiler page. ® ...

Page 26

... Figure 3–2 on page 3–3 FIR Compiler User Guide shows the default values for a low pass filter. © December 2010 Altera Corporation Chapter 3: Parameter Settings Specifying the Coefficients ...

Page 27

... Generator dialog box to make the settings listed in Table 3–1. Coefficients Generator Parameter Settings for a Simple Parallel Filter Parameter Rate Specification Filter Type Coefficients Cutoff Freq. 1 Window Type Sample Rate: Cutoff Freq. 2 © December 2010 Altera Corporation Table 3–1. Value Single Rate Band Pass 77 5e+006 Hamming 50e+006 ...

Page 28

... For an explanation of interpolation and decimation, refer to Decimation” on page FIR Compiler User Guide shows a decimation filter. The cut-off frequency is ¼ of the 4–8. © December 2010 Altera Corporation Chapter 3: Parameter Settings Specifying the Coefficients “Interpolation and ...

Page 29

... You can click the Time Response & Coefficient Values tab to list the coefficients as shown in © December 2010 Altera Corporation (Figure 3–1 on page Figure 3–5 on page 3–6. ...

Page 30

... Click New Coefficient Set in the Parameterize - FIR Compiler page on page 3–2); then select Imported Coefficient Set in the Coefficients Generator dialog box FIR Compiler User Guide (Figure 3–6 on page 3–7). Chapter 3: Parameter Settings Specifying the Coefficients (Figure 3–1 © December 2010 Altera Corporation ...

Page 31

... Do not insert additional carriage returns at the end of the file. The FIR Compiler interprets each carriage return as an extra coefficient with the value of the most recent past coefficient. The file should have a minimum of five non-zero coefficients. 3. Click OK to import your coefficient set. © December 2010 Altera Corporation 3–7 FIR Compiler User Guide ...

Page 32

... Chapter 3: Parameter Settings Analyzing the Coefficients Original input data Original coefficient data Full precision after FIR calculation Output data after limiting precision + © December 2010 Altera Corporation ...

Page 33

... Specify the Input and Output Specifications You can specify the Number of Input Channels (that is, the number of data streams that generate an output for each stream) and the Input Number System in the Parameterize - FIR Compiler page © December 2010 Altera Corporation (Figure 3–7). FIR Compiler User Guide ...

Page 34

... Limited Full Limited Precision Precision Precision Chapter 3: Parameter Settings Specify the Input and Output Specifications Result (Figure 3–8). Bits Removed from both MSB & LSB D15 D14 D13 D10 D9 D12 . . . . . . Full Limited Precision Precision © December 2010 Altera Corporation ...

Page 35

... For more information about the filter architectures and how they operate, refer to “FIR Compiler” on page © December 2010 Altera Corporation Area Speed (Data Throughput) Creates a fast filter: 140 to over 300 MSPS throughput with pipelining in Stratix II devices. ...

Page 36

... When the input data is unsigned, the input data bit width should be greater than or equal to one. When the input data is signed, the input data bit width should be greater than or equal to two. FIR Compiler User Guide 3–5, Table 3–6, and Table 3–7 describe the FIR Compiler options that (Note 1) Description Chapter 3: Parameter Settings Specify the Architecture Specification © December 2010 Altera Corporation ...

Page 37

... Force Non-Symmetric If you want to create a design that uses both symmetric and non-symmetric coefficients, turn on Structure this option. Symmetric algorithms require an extra clock cycle per calculation cycle, which leads to lower throughput. © December 2010 Altera Corporation (Note 1) Description (Note 1) Description 3–13 FIR Compiler User Guide ...

Page 38

... When input data is unsigned, the input data bit width should be greater than or equal to one. When input data is signed, the input data bit width should be greater than or equal to two. FIR Compiler User Guide (Note 1) Description (Note 1) Description Chapter 3: Parameter Settings Specify the Architecture Specification © December 2010 Altera Corporation ...

Page 39

... These settings are shown in Figure 3–9. Figure 3–9. Specify the Filter Architecture 2. Click Finish when you have set the architecture parameters. © December 2010 Altera Corporation 3–15 FIR Compiler User Guide ...

Page 40

... A comb filter is a filter that has repetitive notches. You can make a comb filter by first making a single-notch filter, and then using sub-sampling. The process of sub- sampling reflects or mirrors the notches in the frequency domain at all frequencies above Nyquist. FIR Compiler User Guide Chapter 3: Parameter Settings (Figure 3–10). © December 2010 Altera Corporation Resource Estimates ...

Page 41

... The highest throughput filters are parallel filters with extended pipelining that generate an output for every clock cycle. ■ Altera recommends that you use memory blocks to reduce the area. ■ The FIR filter typically runs at a higher f set_global_assignment -name "PHYSICAL_SYNTHESIS_COMBO_LOGIC" "ON" ...

Page 42

... FIR Compiler User Guide Chapter 3: Parameter Settings Filter Design Tips © December 2010 Altera Corporation ...

Page 43

... The FIR Compiler automatically creates coefficients (with a user-specified number of taps) for the following filters: ■ Low Pass ■ High Pass Band Pass ■ © December 2010 Altera Corporation 4. Functional Description FIR Compiler User Guide ...

Page 44

... None—The FIR Compiler can read in pre-scaled integer values for the coefficients and not apply scaling factors. FIR Compiler User Guide Figure 3–2 on page 3–3. Figure 3–5 on page Chapter 4: Functional Description FIR Compiler 3–6. © December 2010 Altera Corporation ...

Page 45

... Because non-symmetrical serial FIR filters do not require this resource, non- symmetrical filters may be smaller and/or faster. You can use the Resource Estimator in the Architecture Specification area of the Parameterize FIR Compiler page to determine the best solution available. Refer to Figure 3–9 on page © December 2010 Altera Corporation Figure 4– ...

Page 46

... You should include the directory path with the input and output coefficient file names, as indicated above. FIR Compiler User Guide - Data Out Chapter 4: Functional Description FIR Compiler - © December 2010 Altera Corporation ...

Page 47

... The reloading capability allows you to change coefficient values. These filters may contain optimizations for symmetrical filters. If you want a filter that may need both symmetrical and non-symmetrical filters, turn on Force Non-Symmetrical Structures in the Architecture Specification section of the Parameterize FIR Compiler page. © December 2010 Altera Corporation 4–5 FIR Compiler User Guide ...

Page 48

... MHz at the cost of pipeline latency. Figure 4–3 shows the parallel filter block diagram. Figure 4–3. Parallel Filter Block Diagram xin FIR Compiler User Guide Array Multiplier yout Chapter 4: Functional Description FIR Compiler 4–4. xout Array Multiplier © December 2010 Altera Corporation ...

Page 49

... FIR result. This structure provides greater throughput than a standard serial structure while using less area than a fully parallel structure, allowing you to trade off device area for speed. Figure 4–5 shows the multibit serial structure. Figure 4–5. Multibit Serial Structure © December 2010 Altera Corporation ...

Page 50

... This means that the input data is multiplied by a different set of coefficients and the filter results are different. FIR Compiler User Guide Chapter 4: Functional Description With Extended Parallel Pipelining Multi-Bit With Extended Serial Pipelining With Extended Serial Pipelining Area © December 2010 Altera Corporation FIR Compiler ...

Page 51

... Using the low-level optimization technique, the polyphase decomposed filter is implemented using a multichannel, multiple coefficient set structure with an appropriate wrapper. © December 2010 Altera Corporation (Figure 4–7). Input N LPF Input ...

Page 52

... FIR Compiler User Guide 4–14 illustrate the results when applying polyphase decomposition to output output input shows a decimation filter (with polyphase decomposition). Chapter 4: Functional Description FIR Compiler N Channel N Coefficient Set output Single Rate FIR Filter Control Circuitry © December 2010 Altera Corporation ...

Page 53

... Stratix IV, Stratix III and Stratix II filters implement ternary adder structures in all architectures: Fully parallel distributed arithmetic ■ Fully serial distributed arithmetic ■ ■ Multibit serial distributed arithmetic ■ Multicycle variable © December 2010 Altera Corporation output N N Channel output N Coefficient Set input Single Rate FIR Filter Control Circuitry 4– ...

Page 54

... Pipelining breaks long carry chains into shorter lengths. Therefore, if the carry chains in your design are already short, adding pipelining may not speed your design. The FIR Compiler lets you select whether to add one, two, or three pipeline levels. FIR Compiler User Guide Chapter 4: Functional Description FIR Compiler © December 2010 Altera Corporation ...

Page 55

... Avalon-ST interface. parameters that are defined for the Avalon-ST interfaces used by the FIR Compiler. All parameters not explicitly listed in the table have undefined values. © December 2010 Altera Corporation Table 2–1 on page 2–6 Table 4–1 on page 4–14 lists the values of these 4– ...

Page 56

... Data Source valid data error channel startofpacket endofpacket Chapter 4: Functional Description Avalon Streaming Interface Value Direction Sink to Source Source to Sink Source to Sink Source to Sink Source to Sink Source to Sink Source to Sink Avalon Interface Data Sink ready © December 2010 Altera Corporation ...

Page 57

... Figure 4–13. Packet Data Transfer 1 clk ready valid startofpacket endofpacket channel[1:0] error[1:0] data 1 The channel input signal is not used in the FIR Compiler interface. © December 2010 Altera Corporation ...

Page 58

... Missing EOP ■ 11: Unexpected EOP ■ Other types of errors are also marked as 11. Asserted by the downstream module able to accept data. Asserted by the FIR filter when there is valid data to output. Chapter 4: Functional Description Signals Figure 4–11 packet error is © December 2010 Altera Corporation ...

Page 59

... All timing diagrams assume a full streaming operation where ast_source_ready and ast_sink_ready are always 1 (unless otherwise stated). © December 2010 Altera Corporation Indicates the index of the channel whose result is presented at the data output. The width of this signal = log (number of channels) ...

Page 60

... FIR filter implemented either in MCV architecture with a Clocks to Compute value Parallel architecture. Figure 4–15. Single Channel, Single Rate (Parallel or MCV Single Cycle) FIR Compiler User Guide Chapter 4: Functional Description Timing Diagrams © December 2010 Altera Corporation ...

Page 61

... For an MCV multicycle filter the clocks to compute value ■ For a Multibit Serial filter (input data bit width)/(number of serial units) ■ ■ For a Serial filter (input data bit width +1) © December 2010 Altera Corporation Figure 4–15. Figure 4–18 on page 4–20 demonstrate another single channel, single 4–19 ...

Page 62

... Interpolation Filter Timing Diagrams Figure 4–19 and filter with a parallel architecture. Figure 4–19. Single Channel, Interpolation-by-2 (Parallel, MCV Single Cycle), ast_sink_valid Control FIR Compiler User Guide Figure 4–20 on page 4–21 show a single channel interpolation-by-2 Chapter 4: Functional Description Timing Diagrams © December 2010 Altera Corporation ...

Page 63

... In a decimation-by-M filter, for every M input data, one output will be produced. Figure 4–22 on page 4–22 by-2 filter, new input data is taken each clock cycle and new output data is produced every other clock cycle. © December 2010 Altera Corporation Figure 4–19. and Figure 4– ...

Page 64

... The first data to reload in each memory block is always zero. The rising edge of the coef_we signal resets the internal data address counter for reloading. FIR Compiler User Guide Chapter 4: Functional Description Timing Diagrams © December 2010 Altera Corporation ...

Page 65

... In the algorithm, look-up tables store partial products of the coefficient; the first data of the partial product is always 0. When reloading pre-calculated coefficients in serial, multibit serial, and parallel architectures, the first reloading coefficient is always 0. For information about how to pre-calculate coefficients, refer to Reloading and Reordering” on page © December 2010 Altera Corporation 4– ...

Page 66

... Coef_we is valid one clock cycle after effective coef_ld 0 -114 - Input coefficients coef_in are sequence adjusted coef_we is effective two clock cycles before first coef_in data 0 5 -114 -12 0 Chapter 4: Functional Description Timing Diagrams -10 0 -16 -127 -16 -10 0 -16 -127 -16 -16 8 Coefficients from © December 2010 Altera Corporation ...

Page 67

... Figure 4–29. Timing Requirements for Loading Multiple Coefficient Sets clk ast_sink_ready ast_sink_data coef_we coef_in 0 coef_set coef_set_in ast_source_valid ast_source_data coef_set_in must be sustained one clock cycle longer than coef_we © December 2010 Altera Corporation (Figure 4–28). This data is calculated with coef_set1 113 - Figure 4– ...

Page 68

... Referenced Documents Altera application notes, white papers, and user guides providing more detailed explanations of how to effectively design with MegaCore functions and the Quartus II software are available at the Altera web site (www.altera.com). In particular, refer to the following references: MegaCore IP Library Release Notes and ■ ...

Page 69

... Coefficient must of serial be in memory) units) ≥ 4 Decimation (Reloadable (number Coefficient must of serial be in memory) units) © December 2010 Altera Corporation A. FIR Compiler Supported Device Flow Data Coefficient Control Storage Avalon-ST Logic cell, M512, Logic cell, interface and M4K, M-RAM M512, M4K, ...

Page 70

... M144K, Auto MLAB, M9K, clock enable Auto Supported Device Structures Multiple Coefficient Symmetric Storage Sets Coefficient Yes Yes Yes Yes Yes N/A Yes N/A Yes Yes Yes Yes Yes Yes Yes N/A Yes Yes © December 2010 Altera Corporation ...

Page 71

... integer) These files are created by the FIR Compiler and are stored in the project directory you specified when you ran the FIR Compiler. © December 2010 Altera Corporation ® II software selects M512 or M4K) and the “Coefficient Reloading and Reordering” on page A– ...

Page 72

... A–4 FIR Compiler User Guide Appendix A: FIR Compiler Supported Device Structures HardCopy II Support © December 2010 Altera Corporation ...

Page 73

... Added information to support new features ■ Preliminary support for Stratix II GX and HardCopy II ■ Updated screenshots ■ Updated many timing diagrams in Chapter 3 ■ © December 2010 Altera Corporation Additional Information Changes Made ® ® III devices ® III devices ® ...

Page 74

... Product literature Non-technical support (General) (Software Licensing) Email Note to table: (1) You can also contact your local Altera sales office or sales representative. Typographic Conventions This document uses the typographic conventions shown in the following table. Visual Cue Bold Type with Initial Capital Letters ...

Page 75

... December 2010 Altera Corporation Meaning Quotation marks indicate references to sections within a document and titles of Quartus II Help topics. For example, “Typographic Conventions.” Indicates signal, port, register, bit, block, and primitive names. For example, data1, tdi, and input Active-low signals are denoted by suffix n. Example: resetn. ...

Page 76

... Info–4 FIR Compiler User Guide Additional Information Typographic Conventions © December 2010 Altera Corporation ...