IPR-CRC Altera, IPR-CRC Datasheet - Page 14

IPR-CRC

Manufacturer Part Number

IPR-CRC

Description

IP CORE Renewal Of IP-CRC

Manufacturer

Altera

Datasheet

1.IP-CRC.pdf

(30 pages)

Specifications of IPR-CRC

Software Application

IP CORE, Interface And Protocols, COMMUNICATION

Supported Families

Arria GX, Cyclone, HardCopy, Stratix

Core Architecture

FPGA

Core Sub-architecture

Arria, Cyclone, Stratix

Rohs Compliant

NA

Lead Free Status / RoHS Status

na

2–4

Set Up Simulation

CRC Compiler User Guide

c

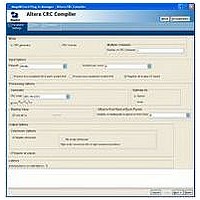

Figure 2–1

Figure 2–1. Parameters Setting Page

To generate a simulation model or a netlist, click Next (or the EDA tab) to display the

EDA page. Turn on the options as required.

An IP functional simulation model is a cycle-accurate VHDL or Verilog HDL model

produced by the Quartus II software. The model allows for fast functional simulation

of IP using industry-standard VHDL and Verilog HDL simulators.

You may only use these models for simulation and expressly not for synthesis or any

other purposes. Using these models for synthesis creates a nonfunctional design.

To generate an IP functional simulation model for your MegaCore function, follow

these steps:

1. Turn on Generate Simulation Model.

2. Click Next (or the Summary tab) to display the Summary page.

You can use the check boxes on the Summary page to enable or disable the generation

of specified files. A gray checkmark indicates a file that is automatically generated;

other files are optional.

1

Some third-party synthesis tools can use a netlist that contains only the

structure of the MegaCore function, but not detailed logic, to optimize

performance of the design that contains the MegaCore function. Turn on

Generate netlist only if your synthesis tool supports this feature.

shows you the Parameter Settings page.

Preliminary

© November 2009 Altera Corporation

Chapter 2: Getting Started

CRC Compiler Walkthrough