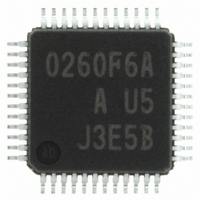

M30260F6AGP#U5A Renesas Electronics America, M30260F6AGP#U5A Datasheet - Page 37

M30260F6AGP#U5A

Manufacturer Part Number

M30260F6AGP#U5A

Description

IC M16C MCU FLASH 48K 48LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/Tiny/26r

Datasheet

1.M30260F3AGPU5A.pdf

(354 pages)

Specifications of M30260F6AGP#U5A

Core Processor

M16C/60

Core Size

16-Bit

Speed

20MHz

Connectivity

I²C, IEBus, SIO, UART/USART

Peripherals

DMA, PWM, Voltage Detect, WDT

Number Of I /o

39

Program Memory Size

48KB (48K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

48-LQFP

Cpu Family

R8C

Device Core Size

16b

Frequency (max)

20MHz

Interface Type

UART

Total Internal Ram Size

2KB

# I/os (max)

39

Number Of Timers - General Purpose

8

Operating Supply Voltage (typ)

3.3/5V

Operating Supply Voltage (max)

5.5V

Operating Supply Voltage (min)

3V

On-chip Adc

12-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-20C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

48

Package Type

LQFP

Package

48LQFP

Family Name

R8C

Maximum Speed

20 MHz

Operating Supply Voltage

3.3|5 V

Data Bus Width

16 Bit

Number Of Programmable I/os

39

Number Of Timers

8

For Use With

R0K33026AS000BE - KIT DEV EVALUATION M16C/26A

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

M30260F6AGP#U5AM30260F6AGP#D3

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

M30260F6AGP#U5AM30260F6AGP#U3

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

M30260F6AGP#U5AM30260F6AGP#U3A

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 37 of 354

- Download datasheet (4Mb)

M

R

R

e

E

1

. v

2.3 Frame Base Register (FB)

2.4 Interrupt Table Register (INTB)

2.5 Program Counter (PC)

2.6 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

2.7 Static Base Register (SB)

2.8 Flag Register (FLG)

J

6

0

FB is configured with 16 bits, and is used for FB relative addressing.

INTB is configured with 20 bits, indicating the start address of an interrupt vector table.

PC is configured with 20 bits, indicating the address of an instruction to be executed.

Stack pointer (SP) comes in two types: USP and ISP, each configured with 16 bits.

Your desired type of stack pointer (USP or ISP) can be selected by the U flag of FLG.

SB is configured with 16 bits, and is used for SB relative addressing.

FLG consists of 11 bits, indicating the CPU status.

2.8.1 Carry Flag (C Flag)

2.8.2 Debug Flag (D Flag)

2.8.3 Zero Flag (Z Flag)

2.8.4 Sign Flag (S Flag)

2.8.5 Register Bank Select Flag (B Flag)

2.8.6 Overflow Flag (O Flag)

2.8.7 Interrupt Enable Flag (I Flag)

2.8.8 Stack Pointer Select Flag (U Flag)

2.8.9 Processor Interrupt Priority Level (IPL)

2.8.10 Reserved Area

C

2

9

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

The D flag is used exclusively for debugging purpose. During normal use, it must be set to 0.

This flag is set to 1 when an arithmetic operation resulted in 0; otherwise, it is 0.

This flag is set to 1 when an arithmetic operation resulted in a negative value; otherwise, it is 0.

Register bank 0 is selected when this flag is 0 ; register bank 1 is selected when this flag is 1.

This flag is set to 1 when the operation resulted in an overflow; otherwise, it is 0.

This flag enables a maskable interrupt.

Maskable interrupts are disabled when the I flag is 0, and are enabled when the I flag is 1.

The I flag is cleared to 0 when the interrupt request is accepted.

ISP is selected when the U flag is 0; USP is selected when the U flag is 1.

The U flag is cleared to 0 when a hardware interrupt request is accepted or an INT instruction for software

interrupt Nos. 0 to 31 is executed.

IPL is configured with three bits, for specification of up to eight processor interrupt priority levels from level

0 to level 7.

If a requested interrupt has priority greater than IPL, the interrupt is enabled.

When write to this bit, write 0. When read, its content is undefined.

0 .

2 /

B

0

0

6

2

A

0

F

2

e

G

0 -

b

o r

1 .

2

0

u

, 5

0

p

2

(

0

M

0

7

1

6

C

page 18

2 /

6

, A

M

1

f o

6

C

3

2 /

2

9

6

, B

M

1

6

C

2 /

6

) T

2. CPU

Related parts for M30260F6AGP#U5A

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: