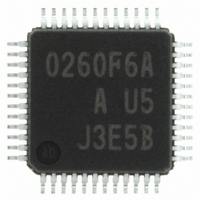

M30260F6AGP#U5A Renesas Electronics America, M30260F6AGP#U5A Datasheet - Page 185

M30260F6AGP#U5A

Manufacturer Part Number

M30260F6AGP#U5A

Description

IC M16C MCU FLASH 48K 48LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/Tiny/26r

Datasheet

1.M30260F3AGPU5A.pdf

(354 pages)

Specifications of M30260F6AGP#U5A

Core Processor

M16C/60

Core Size

16-Bit

Speed

20MHz

Connectivity

I²C, IEBus, SIO, UART/USART

Peripherals

DMA, PWM, Voltage Detect, WDT

Number Of I /o

39

Program Memory Size

48KB (48K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

48-LQFP

Cpu Family

R8C

Device Core Size

16b

Frequency (max)

20MHz

Interface Type

UART

Total Internal Ram Size

2KB

# I/os (max)

39

Number Of Timers - General Purpose

8

Operating Supply Voltage (typ)

3.3/5V

Operating Supply Voltage (max)

5.5V

Operating Supply Voltage (min)

3V

On-chip Adc

12-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-20C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

48

Package Type

LQFP

Package

48LQFP

Family Name

R8C

Maximum Speed

20 MHz

Operating Supply Voltage

3.3|5 V

Data Bus Width

16 Bit

Number Of Programmable I/os

39

Number Of Timers

8

For Use With

R0K33026AS000BE - KIT DEV EVALUATION M16C/26A

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

M30260F6AGP#U5AM30260F6AGP#D3

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

M30260F6AGP#U5AM30260F6AGP#U3

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

M30260F6AGP#U5AM30260F6AGP#U3A

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 185 of 354

- Download datasheet (4Mb)

R

R

M

e

E

1

. v

J

6

0

C

2

9

0 .

B

2 /

0

0

13.1.3.4 Transfer Clock

13.1.3.5 SDA Output

13.1.3.6 SDA Input

6

2

A

0

F

Data is transmitted/received using a transfer clock like the one shown in Figure 13.1.3.2.1.

The CSC bit in the U2SMR2 register is used to synchronize the internally generated clock (internal

SCL2) and an external clock supplied to the SCL

synchronization enabled), if a falling edge on the SCL

the internal SCL

ing in the low-level interval. If the internal SCL

low, counting stops, and when the SCL

In this way, the UART2 transfer clock is comprised of the logical product of the internal SCL

pin signal. The transfer clock works from a half period before the falling edge of the internal SCL

bit to the rising edge of the 9

The SWC bit in the U2SMR2 register allows to select whether the SCL

from low-level output at the falling edge of the 9th clock pulse.

If the SCLHI bit in the U2SMR4 register is set to “1” (enabled), SCL

high-impedance state) when a stop condition is detected.

Setting the SWC2 bit in the U2SMR2 register is set to "1" (0 output) makes it possible to forcibly output

a low-level signal from the SCL

(transfer clock) allows the transfer clock to be output from or supplied to the SCL

outputting a low-level signal.

If the SWC9 bit in the U2SMR4 register is set to “1” (SCL hold low enabled) when the CKPH bit in the

U2SMR3 register is set to "1", the SCL

pulse next to the ninth. Setting the SWC9 bit is set to "0" (SCL hold low disabled) frees the SCL

from low-level output.

The data written to the bit 7 to bit 0 (D

D

The initial value of SDA

the SMD2 to SMD0 bits in the the U2MR register are set to ‘000

The DL2 to DL0 bits in the U2SMR3 register allow to add no delays or a delay of 2 to 8 U2BRG count

source clock cycles to SDA

Setting the SDHI bit in the U2SMR2 register is set to "1" (SDA output disabled) forcibly places the

SDA

of the UART2 transfer clock. This is because the ABT bit may inadvertently be set to “1” (detected).

When the IICM2 bit is set to "0", the 1st to 8th bits (D

bit 0 in the U2RB register. The 9th bit (D

When the IICM2 bit is set to "1", the 1st to 7th bits (D

bit 0 in the U2RB register and the 8th bit (D

IICM2 bit is set to "1", providing the CKPH bit to "1", the same data as when the IICM2 bit is set to "0"

can be read out by reading the U2RB register after the rising edge of the corresponding clock pulse of

9th bit.

2

e

G

7

0 -

b

. The ninth bit (D

1 .

o r

2

2

0

, 5

u

0

pin in the high-impedance state. Do not write to the SDHI bit synchronously with the rising edge

p

2

(

0

M

0

7

1

6

C

page 166

2 /

2

6

goes low, at which time the U2BRG register value is reloaded with and starts count-

, A

8

) is ACK or NACK.

M

1

2

f o

6

transmit output can only be set when IICM is set to "1" (I

C

3

2

2 /

2

9

th

output.

6

, B

2

bit. To use this function, select an internal clock for the transfer clock.

pin even while sending or receiving data. Clearing the SWC2 bit to “0”

M

1

6

7

C

to D

2

2

2 /

pin is fixed to low-level output at the falling edge of the clock

8

pin goes high, counting restarts.

6

) is ACK or NACK.

0

0

) T

) in the U2TB register is sequentially output beginning with

) is stored in the bit 8 in the U2RB register. Even when the

2

changes state from low to high while the SCL

2

pin. In cases when the CSC bit is set to “1” (clock

7

7

2

to D

to D

pin is detected while the internal SCL

0

1

) of received data are stored in the bit 7 to

) of received data are stored in the bit 6 to

2

’ (serial I/O disabled).

2

output is turned off (placed in the

2

pin should be fixed to or freed

2

C Bus mode) and

2

pin, instead of

2

13. Serial I/O

and SCL

2

is high,

2

pin is

2

2

1st

pin

2

Related parts for M30260F6AGP#U5A

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: