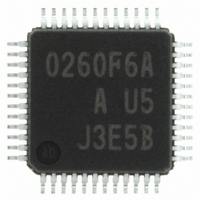

M30260F6AGP#U5A Renesas Electronics America, M30260F6AGP#U5A Datasheet - Page 172

M30260F6AGP#U5A

Manufacturer Part Number

M30260F6AGP#U5A

Description

IC M16C MCU FLASH 48K 48LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/Tiny/26r

Datasheet

1.M30260F3AGPU5A.pdf

(354 pages)

Specifications of M30260F6AGP#U5A

Core Processor

M16C/60

Core Size

16-Bit

Speed

20MHz

Connectivity

I²C, IEBus, SIO, UART/USART

Peripherals

DMA, PWM, Voltage Detect, WDT

Number Of I /o

39

Program Memory Size

48KB (48K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

48-LQFP

Cpu Family

R8C

Device Core Size

16b

Frequency (max)

20MHz

Interface Type

UART

Total Internal Ram Size

2KB

# I/os (max)

39

Number Of Timers - General Purpose

8

Operating Supply Voltage (typ)

3.3/5V

Operating Supply Voltage (max)

5.5V

Operating Supply Voltage (min)

3V

On-chip Adc

12-chx10-bit

Instruction Set Architecture

CISC

Operating Temp Range

-20C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

48

Package Type

LQFP

Package

48LQFP

Family Name

R8C

Maximum Speed

20 MHz

Operating Supply Voltage

3.3|5 V

Data Bus Width

16 Bit

Number Of Programmable I/os

39

Number Of Timers

8

For Use With

R0K33026AS000BE - KIT DEV EVALUATION M16C/26A

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

M30260F6AGP#U5AM30260F6AGP#D3

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

M30260F6AGP#U5AM30260F6AGP#U3

Manufacturer:

Renesas Electronics America

Quantity:

10 000

Part Number:

M30260F6AGP#U5AM30260F6AGP#U3A

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 172 of 354

- Download datasheet (4Mb)

R

R

M

e

E

. v

1

J

Figure 13.1.2.1. Typical transmit timing in UART mode (UART0, UART1)

0

6

• Example of transmit timing when transfer data is 9 bits long (parity disabled, two stop bits)

• Example of transmit timing when transfer data is 8 bits long (parity enabled, one stop bit)

2

9

C

0 .

B

2 /

The above timing diagram applies to the case where the register bits are set

as follows:

Transfer clock

UiC1 register

TI bit

CTSi

TxDi

UiC1 register

TE bit

UiC0 register

TXEPT bit

SiTIC register

IR bit

0

0

• Set the PRYE bit in the UiMR register to "1" (parity enabled)

• Set the STPS bit in the UiMR register to "0" (1 stop bit)

• Set the CRD bit in the UiC0 register to "0" (CTS/RTS enabled),

• Set the UiIRS bit to "1" (an interrupt request occurs when transmit completed):

2

6

Transfer clock

TxDi

The above timing diagram applies to the case where the register bits are set

as follows:

UiC1 register

TE bit

UiC1 register

TI bit

UiC0 register

TXEPT bit

SiTIC register

IR bit

the CRS bit to "0" (CTS selected)

0

A

• Set the PRYE bit in the UiMR register to "0" (parity disabled)

• Set the STPS bit in the UiMR register to "1" (2 stop bits)

• Set the CRD bit in the UiC0 register to "1"(CTS/RTS disabled)

• Set the UiIRS bit to "0" (an interrupt request occurs when transmit buffer

F

U0IRS bit is the UCON register bit 0, U1IRS bit is the UCON

register bit 1, and U2IRS bit is the U2C1 register bit 4

2

becomes empty):

e

U0IRS bit is the UCON register bit 0, U1IRS bit is the UCON

register bit 1, and U2IRS bit is the U2C1 register bit 4

0 -

G

b

1 .

2

o r

0

, 5

u

0

p

2

0

(

0

M

7

“H”

“1”

“0”

“1”

“0”

“L”

“1”

“0”

“1”

“0”

1

“1”

“0”

“1”

“0”

“1”

“0”

“1”

“0”

6

C

page 153

2 /

6

, A

Start

Start

ST

ST

bit

bit

M

Write data to the UiTB register

D

D

1

f o

0

0

Cleared to “0” when interrupt request is accepted, or cleared to “0” in a program

Write data to the UiTB register

6

D

D

3

C

1

1

2

Tc

2 /

9

D

D

2

2

6

, B

D

D

3

3

Tc

D

D

M

4

4

The transfer clock stops momentarily as CTSi is “H” when the stop bit is checked.

The transfer clock starts as the transfer starts immediately CTSi changes to “L”.

1

D

D

6

5

5

C

D

D

6

6

2 /

Transferred from UiTB register to UARTi transmit register

D

D

6

7

7

Parity

) T

bit

D

P

8

Cleared to “0” when interrupt request is accepted, or cleared to “0” in a program

Stop

bit

SP

Stop

bit

SP

SP

Stop

bit

ST

Tc = 16 (n + 1) / fj or 16 (n + 1) / f

Tc = 16 (n + 1) / fj or 16 (n + 1) / f

ST

D

D

0

Transferred from UiTB register to UARTi

transmit register

fj : frequency of UiBRG count source (f

f

n : value set to UiBRG

i: 0 to 2

fj : frequency of UiBRG count source (f

f

n : value set to UiBRG

i: 0 to 2

EXT

EXT

0

D

D

1

1

: frequency of UiBRG count source (external clock)

: frequency of UiBRG count source (external clock)

D

D

2

2

D

D

3

3

D

D

4

4

D

D

5

5

D

D

6

6

D

D

7

EXT

EXT

7

P SP

D

8

SPSP

1SIO

1SIO

Stopped pulsing

because the TE bit

= “0”

ST

, f

, f

2SIO

2SIO

ST

D

0

, f

, f

D

D

8SIO

8SIO

0

1

D

13. Serial I/O

1

, f

, f

32SIO

32SIO

)

)

Related parts for M30260F6AGP#U5A

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: