CY8C3244LTI-130 Cypress Semiconductor Corp, CY8C3244LTI-130 Datasheet - Page 60

CY8C3244LTI-130

Manufacturer Part Number

CY8C3244LTI-130

Description

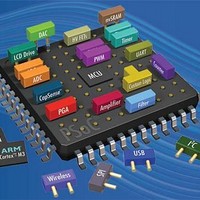

PSOC3

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C32xxr

Datasheet

1.CY8C3244LTI-130T.pdf

(120 pages)

Specifications of CY8C3244LTI-130

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

50MHz

Number Of I /o

38

Eeprom Size

512 x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

2K x 8

Program Memory Size

16KB (16K x 8)

Data Converters

A/D 2x12b, D/A 1x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, POR, PWM, WDT

Connectivity

EBI/EMI, I²C, LIN, SPI, UART/USART

Core Size

8-Bit

Processor Series

CY8C32

Core

8051

Data Bus Width

32 bit

Data Ram Size

2 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

46

Number Of Timers

4

Operating Supply Voltage

1.71 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

38

Eeprom Memory Size

0.5KB

Ram Memory Size

2KB

Cpu Speed

50MHz

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

CY8C3244LTI-130

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Document Number: 001-56955 Rev. *K

1

2

3

4

5

6

7

The voltage levels of Host Programmer and the PSoC 3 voltage domains involved in Programming should be same. The

Port 1 JTAG pins, XRES pin (XRES_N or P1[2]) are powered by V

level as host V

host Programmer.

the capability to toggle power (Vddd, Vdda, All Vddio’s) to PSoC 3. This may typically require external

interface circuitry to toggle power which will depend on the programming setup. The power supplies can

be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other

supplies.

using the TMS,TCK,TDI, TDO pins of PSoC 3, and writing to a specific register. But this requires that the DPS setting in

NVL is not equal to “Debug Ports Disabled”.

unidirectional. But if the DPS setting is changed to non-JTAG mode, the TMS pin in JTAG is bi-directional as the SWD

Protocol has to be used for acquiring the PSoC 3 device initially. After switching from SWD to JTAG mode, the TMS pin

will be uni-directional. In such a case, unidirectional buffer should not be used on TMS line.

the default setting is 4-wire JTAG (nTRST disabled). Use the TMS, TCK pins to do a reset of JTAG TAP controller.

pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48-pin

devices, but use dedicated XRES pin for rest of devices.

Vdda must be greater than or equal to all other power supplies (Vddd, Vddio’s) in PSoC 3.

For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have

For JTAG Programming, Device reset can also be done without connecting to the XRES pin or Power cycle mode by

By default, PSoC 3 is configured for 4-wire JTAG mode unless user changes the DPS setting. So the TMS pin is

nTRST JTAG pin (P1[5]) cannot be used to reset the JTAG TAP controlller during first time programming of PSoC 3 as

If XRES pin is used by host, P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES

Host Programmer

Figure 9-1. JTAG Interface Connections between PSoC 3 and Programmer

DD

. Rest of PSoC 3 voltage domains ( V

nTRST

TMS

XRES

GND

TDO

TDI

TCK

V

DD

5

6

V

DD

GND

DDD

, V

DDA

, V

DDIO0

DDIO1

, V

DDIO2

. So, V

, V

V

TMS (P1[0])

V

TDO (P1[3])

XRES or P1[2]

TDI (P1[4])

nTRST (P1[5])

SSD

TCK (P1[1]

DDD

DDIO3

DDIO1

, V

, V

) need not be at the same voltage level as

SSA

DDA

of PSoC 3 should be at same voltage

PSoC

, V

DDIO0

5

4, 7

PSoC 3

, V

6

DDIO1

®

, V

3: CY8C32 Family

DDIO2

, V

DDIO3

1, 2, 3, 4

Data Sheet

Page 60 of 120