CY8C3244LTI-130 Cypress Semiconductor Corp, CY8C3244LTI-130 Datasheet - Page 47

CY8C3244LTI-130

Manufacturer Part Number

CY8C3244LTI-130

Description

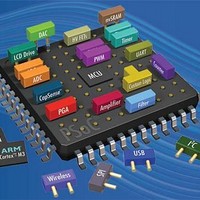

PSOC3

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C32xxr

Datasheet

1.CY8C3244LTI-130T.pdf

(120 pages)

Specifications of CY8C3244LTI-130

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

50MHz

Number Of I /o

38

Eeprom Size

512 x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

2K x 8

Program Memory Size

16KB (16K x 8)

Data Converters

A/D 2x12b, D/A 1x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, POR, PWM, WDT

Connectivity

EBI/EMI, I²C, LIN, SPI, UART/USART

Core Size

8-Bit

Processor Series

CY8C32

Core

8051

Data Bus Width

32 bit

Data Ram Size

2 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

46

Number Of Timers

4

Operating Supply Voltage

1.71 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

38

Eeprom Memory Size

0.5KB

Ram Memory Size

2KB

Cpu Speed

50MHz

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

CY8C3244LTI-130

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

7.2.3.2 Clock Generation

Each subcomponent block of a UDB including the two PLDs, the

datapath, and Status and Control, has a clock selection and

control block. This promotes a fine granularity with respect to

allocating clocking resources to UDB component blocks and

allows unused UDB resources to be used by other functions for

maximum system efficiency.

7.3 UDB Array Description

Figure 7-11

the array core, there are a DSI routing interfaces at the top and

bottom of the array. Other interfaces that are not explicitly shown

include the system interfaces for bus and clock distribution. The

UDB array includes multiple horizontal and vertical routing

channels each comprised of 96 wires. The wire connections to

UDBs, at horizontal/vertical intersection and at the DSI interface

are highly permutable providing efficient automatic routing in

PSoC Creator. Additionally the routing allows wire by wire

segmentation along the vertical and horizontal routing to further

increase routing flexibility and capability.

Figure 7-11. Digital System Interface Structure

7.3.1 UDB Array Programmable Resources

Figure 7-12

a bank of 16 UDBs. The primary programmable resources of the

UDB are two PLDs, one datapath and one status/control register.

These resources are allocated independently, because they

have independently selectable clocks, and therefore unused

blocks are allocated to other unrelated functions.

Document Number: 001-56955 Rev. *K

UDB

UDB

UDB

UDB

HV

HV

HV

HV

shows an example of a 16 UDB array. In addition to

B

A

B

A

shows an example of how functions are mapped into

UDB

UDB

UDB

UDB

System Connections

System Connections

HV

HV

HV

HV

A

B

A

B

UDB

UDB

UDB

UDB

HV

HV

HV

HV

B

A

B

A

UDB

UDB

UDB

UDB

HV

HV

HV

HV

A

B

A

B

An example of this is the 8-bit Timer in the upper left corner of

the array. This function only requires one datapath in the UDB,

and therefore the PLD resources may be allocated to another

function. A function such as a Quadrature Decoder may require

more PLD logic than one UDB can supply and in this case can

utilize the unused PLD blocks in the 8-bit Timer UDB.

Programmable resources in the UDB array are generally

homogeneous so functions can be mapped to arbitrary

boundaries in the array.

Figure 7-12. Function Mapping Example in a Bank of UDBs

7.4 DSI Routing Interface Description

The DSI routing interface is a continuation of the horizontal and

vertical routing channels at the top and bottom of the UDB array

core. It provides general purpose programmable routing

between device peripherals, including UDBs, I/Os, analog

peripherals, interrupts, DMA and fixed function peripherals.

Figure 7-13

interconnect, which connects the UDB array routing matrix with

other device peripherals. Any digital core or fixed function

peripheral that needs programmable routing is connected to this

interface.

Signals in this category include:

8-Bit

Timer

I2C Slave

UART

Interrupt requests from all digital peripherals in the system.

DMA requests from all digital peripherals in the system.

Digital peripheral data signals that need flexible routing to I/Os.

Digital peripheral data signals that need connections to UDBs.

Connections to the interrupt and DMA controllers.

Connection to I/O pins.

Connection to analog system digital signals.

UDB

UDB

UDB

UDB

Quadrature Decoder

HV

HV

illustrates the concept of the digital system

A

B

8-Bit SPI

UDB

UDB

UDB

UDB

PSoC

HV

HV

B

A

Logic

12-Bit PWM

12-Bit SPI

®

UDB

UDB

UDB

UDB

3: CY8C32 Family

16-Bit

PWM

HV

HV

A

B

16-Bit PYRS

8-Bit

Timer

Data Sheet

UDB

UDB

UDB

UDB

Page 47 of 120

Logic

HV

HV

B

A