CY8C3244LTI-130 Cypress Semiconductor Corp, CY8C3244LTI-130 Datasheet - Page 27

CY8C3244LTI-130

Manufacturer Part Number

CY8C3244LTI-130

Description

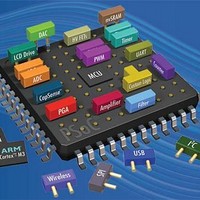

PSOC3

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C32xxr

Datasheet

1.CY8C3244LTI-130T.pdf

(120 pages)

Specifications of CY8C3244LTI-130

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

50MHz

Number Of I /o

38

Eeprom Size

512 x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

2K x 8

Program Memory Size

16KB (16K x 8)

Data Converters

A/D 2x12b, D/A 1x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, POR, PWM, WDT

Connectivity

EBI/EMI, I²C, LIN, SPI, UART/USART

Core Size

8-Bit

Processor Series

CY8C32

Core

8051

Data Bus Width

32 bit

Data Ram Size

2 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

46

Number Of Timers

4

Operating Supply Voltage

1.71 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

38

Eeprom Memory Size

0.5KB

Ram Memory Size

2KB

Cpu Speed

50MHz

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

CY8C3244LTI-130

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

Table 6-1. Oscillator Summary

6.1.1 Internal Oscillators

6.1.1.1 Internal Main Oscillator

In most designs the IMO is the only clock source required, due

to its ±1-percent accuracy. The IMO operates with no external

components and outputs a stable clock. A factory trim for each

frequency range is stored in the device. With the factory trim,

tolerance varies from ±1 percent at 3 MHz, up to ±4-percent at

24 MHz. The IMO, in conjunction with the PLL, allows generation

of CPU and system clocks up to the device's maximum

frequency (see

The IMO provides clock outputs at 3, 6, 12, and 24 MHz.

Document Number: 001-56955 Rev. *K

MHzECO

kHzECO

Doubler

Source

IMO

DSI

PLL

ILO

Phase-locked

24 MHz

48 MHz

32 kHz

3 MHz

4 MHz

0 MHz

1 kHz

Fmin

7

3-24 MHz

IMO

Doubler for

Divider 16 bit

Divider 16 bit

Divider 16 bit

Divider 16 bit

±1% over voltage and temperature

Crystal dependent

Input dependent

Input dependent

Input dependent

–50%, +100%

Crystal dependent

Digital Clock

Digital Clock

Digital Clock

Digital Clock

Loop)

48 MHz

USB

4-25 MHz

ECO

Tolerance at Fmin

24-50 MHz

PLL

Figure 6-1. Clocking Subsystem

External IO

0-50 MHz

or DSI

Clock Mux

Divider 16 bit

Divider 16 bit

Divider 16 bit

Divider 16 bit

Digital Clock

Digital Clock

Digital Clock

Digital Clock

System

32 kHz ECO

6.1.1.2 Clock Doubler

The clock doubler outputs a clock at twice the frequency of the

input clock. The doubler works at input frequency of 24 MHz,

providing 48 MHz for the USB. It can be configured to use a clock

from the IMO, MHzECO, or the DSI (external pin).

6.1.1.3 Phase-locked Loop

The PLL allows low-frequency, high-accuracy clocks to be

multiplied to higher frequencies. This is a tradeoff between

higher clock frequency and accuracy and, higher power

consumption and increased startup time.

The PLL block provides a mechanism for generating clock

frequencies based upon a variety of input sources. The PLL

100 kHz

24 MHz

25 MHz

50 MHz

50 MHz

48 MHz

32 kHz

Fmax

1,33,100 kHz

±4%

Crystal dependent

Input dependent

Input dependent

Input dependent

–55%, +100%

Crystal dependent

ILO

Tolerance at Fmax

7

PSoC

CPU Clock Divider

Bus Clock Divider

Analog Clock

Analog Clock

Analog Clock

Analog Clock

Divider 16 bit

Divider 16 bit

Divider 16 bit

Divider 16 bit

®

3: CY8C32 Family

16 bit

4 bit

10 µs max

5 ms typ, max is

crystal dependent

Input dependent

250 µs max

1 µs max

15 ms max in lowest

power mode

500 ms typ, max is

crystal dependent

e

w

e

w

e

w

e

w

s

k

s

k

s

k

s

k

Data Sheet

Startup Time

Clock

CPU

Clock

Bus

Page 27 of 120