CY8C3244LTI-130 Cypress Semiconductor Corp, CY8C3244LTI-130 Datasheet - Page 51

CY8C3244LTI-130

Manufacturer Part Number

CY8C3244LTI-130

Description

PSOC3

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ 3 CY8C32xxr

Datasheet

1.CY8C3244LTI-130T.pdf

(120 pages)

Specifications of CY8C3244LTI-130

Package / Case

*

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Speed

50MHz

Number Of I /o

38

Eeprom Size

512 x 8

Core Processor

8051

Program Memory Type

FLASH

Ram Size

2K x 8

Program Memory Size

16KB (16K x 8)

Data Converters

A/D 2x12b, D/A 1x8b

Oscillator Type

Internal

Peripherals

CapSense, DMA, POR, PWM, WDT

Connectivity

EBI/EMI, I²C, LIN, SPI, UART/USART

Core Size

8-Bit

Processor Series

CY8C32

Core

8051

Data Bus Width

32 bit

Data Ram Size

2 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

50 MHz

Number Of Programmable I/os

46

Number Of Timers

4

Operating Supply Voltage

1.71 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

38

Eeprom Memory Size

0.5KB

Ram Memory Size

2KB

Cpu Speed

50MHz

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

CY8C3244LTI-130

Manufacturer:

CYPRESS/赛普拉斯

Quantity:

20 000

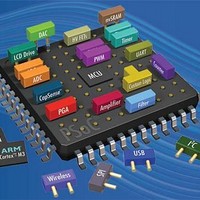

8. Analog Subsystem

The analog programmable system creates application specific

combinations of both standard and advanced analog signal

processing blocks. These blocks are then interconnected to

each other and also to any pin on the device, providing a high

level of design flexibility and IP security. The features of the

analog subsystem are outlined here to provide an overview of

capabilities and architecture.

The PSoC Creator software program provides a user friendly interface to configure the analog connections between the GPIO and

various analog resources and connections from one analog resource to another. PSoC Creator also provides component libraries that

allow you to configure the various analog blocks to perform application specific functions. The tool also generates API interface

libraries that allow you to write firmware that allows the communication between the analog peripheral and CPU/Memory.

Document Number: 001-56955 Rev. *K

Flexible, configurable analog routing architecture provided by

analog globals, analog mux bus, and analog local buses.

GPIO

Port

A

N

A

L

O

G

R

O

U

T

N

G

I

DAC

Figure 8-1. Analog Subsystem Block Diagram

Array

DSI

Distribution

Interface

Analog

Clock

CapSense Subsystem

Comparators

CMP

Registers

Config &

Status

Reference

Precision

CMP

Decimator

High resolution delta-sigma ADC.

One 8-bit DAC that provides either voltage or current output.

Two comparators with optional connection to configurable LUT

outputs.

CapSense subsystem to enable capacitive touch sensing.

Precision reference for generating an accurate analog voltage

for internal analog blocks.

PHUB

PSoC

A

N

A

L

O

G

R

O

U

T

N

G

I

CPU

GPIO

Port

®

3: CY8C32 Family

Data Sheet

Page 51 of 120