A000047 Arduino, A000047 Datasheet - Page 220

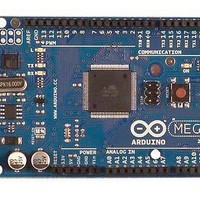

A000047

Manufacturer Part Number

A000047

Description

MCU, MPU & DSP Development Tools Mega2560

Manufacturer

Arduino

Series

-r

Type

MCUr

Specifications of A000047

Processor To Be Evaluated

ATmega2560

Interface Type

USB, I2C, SPI

Dimensions

4 in x 2.1 in

Operating Supply Voltage

5 V

Contents

Board

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

ATmega2560

- Current page: 220 of 444

- Download datasheet (10Mb)

21.7.3

2549M–AVR–09/10

Asynchronous Operational Range

Figure 21-7. Stop Bit Sampling and Next Start Bit Sampling

The same majority voting is done to the stop bit as done for the other bits in the frame. If the stop

bit is registered to have a logic 0 value, the Frame Error (FEn) Flag will be set.

A new high to low transition indicating the start bit of a new frame can come right after the last of

the bits used for majority voting. For Normal Speed mode, the first low level sample can be at

point marked (A) in

(B). (C) marks a stop bit of full length. The early start bit detection influences the operational

range of the Receiver.

The operational range of the Receiver is dependent on the mismatch between the received bit

rate and the internally generated baud rate. If the Transmitter is sending frames at too fast or too

slow bit rates, or the internally generated baud rate of the Receiver does not have a similar (see

Table 21-2 on page

frames to the start bit.

The following equations can be used to calculate the ratio of the incoming data rate and internal

receiver baud rate.

D

S

S

S

R

F

M

slow

(U2X = 0)

(U2X = 1)

Sample

Sample

RxD

R

slow

mode.

for Double Speed mode.

S

receiver baud rate. R

accepted in relation to the receiver baud rate.

Sum of character size and parity size (D = 5 to 10 bit).

Samples per bit. S = 16 for Normal Speed mode and S = 8 for Double Speed

First sample number used for majority voting. S

Middle sample number used for majority voting. S

is the ratio of the slowest incoming data rate that can be accepted in relation to the

=

M

= 5 for Double Speed mode.

------------------------------------------ -

S 1

–

Figure

221) base frequency, the Receiver will not be able to synchronize the

(

D

+

1

1

+

D S ⋅

1

2

21-7. For Double Speed mode the first low level must be delayed to

)S

+

3

2

S

ATmega640/1280/1281/2560/2561

F

4

fast

5

3

is the ratio of the fastest incoming data rate that can be

6

7

4

8

STOP 1

9

5

10

R

fast

(A)

0/1

6

=

0/1

F

-----------------------------------

(

= 8 for normal speed and S

D

(B)

0/1

0/1

(

+

D

M

1

+

= 9 for normal speed and

)S

2

)S

+

S

M

(C)

F

220

= 4

Related parts for A000047

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO UNO PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO SHIELD PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Development Boards & Kits - AVR ARDUINO STARTER KIT W/ UNO REV3

Manufacturer:

Arduino

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS PROTO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS WITH SD

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Development Software Getting started w/Arduino

Manufacturer:

Arduino

Part Number:

Description:

Ethernet Modules & Development Tools Ethernet Shield for Arduino

Manufacturer:

Arduino

Part Number:

Description:

MCU, MPU & DSP Development Tools LilyPad Arduino Main Board

Manufacturer:

Arduino

Part Number:

Description:

ARDUINO NANO Board

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Ethernet Modules & Development Tools ETHERNET SHEILD PoE FOR ARDUINO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

ATMEGA328 MCU IC W/ Arduino UNO Bootloader

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Memory Cards MICRO SD CARD 1GB WITH SD ADAPTER

Manufacturer:

Arduino