C8051F411EK Silicon Laboratories Inc, C8051F411EK Datasheet - Page 112

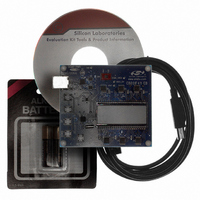

C8051F411EK

Manufacturer Part Number

C8051F411EK

Description

KIT EVAL FOR C8051F411

Manufacturer

Silicon Laboratories Inc

Type

MCUr

Specifications of C8051F411EK

Contents

Evaluation Board, CD-ROM, USB Cable, Batteries and User Guide

Processor To Be Evaluated

C8051F41x

Interface Type

USB

Silicon Manufacturer

Silicon Labs

Core Architecture

8051

Silicon Core Number

C8051F411

Silicon Family Name

C8051F41x

Kit Contents

LCD Based Evaluation Board, USB Cable, Software CD And Quick-Start Guide

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

For Use With/related Products

Silicon Laboratories C8051F41x

For Use With

336-1315 - KIT REF DESIGN VOICE RECORD F41X

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1317

- Current page: 112 of 270

- Download datasheet (2Mb)

C8051F410/1/2/3

12.4. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described below. Refer to the

data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt

conditions for the peripheral and the behavior of its interrupt-pending flag(s).

112

Bit 7:

Bit 6:

Bit 5:

Bit 4:

Bit 3:

Bit 2:

Bit 1:

Bit 0:

R/W

EA

Bit7

EA: Global Interrupt Enable.

This bit globally enables/disables all interrupts. It overrides the individual interrupt mask set-

tings.

0: Disable all interrupt sources.

1: Enable each interrupt according to its individual mask setting.

ESPI0: Enable Serial Peripheral Interface (SPI0) Interrupt.

This bit sets the masking of the SPI0 interrupts.

0: Disable all SPI0 interrupts.

1: Enable interrupt requests generated by SPI0.

ET2: Enable Timer 2 Interrupt.

This bit sets the masking of the Timer 2 interrupt.

0: Disable Timer 2 interrupt.

1: Enable interrupt requests generated by the TF2L or TF2H flags.

ES0: Enable UART0 Interrupt.

This bit sets the masking of the UART0 interrupt.

0: Disable UART0 interrupt.

1: Enable UART0 interrupt.

ET1: Enable Timer 1 Interrupt.

This bit sets the masking of the Timer 1 interrupt.

0: Disable all Timer 1 interrupt.

1: Enable interrupt requests generated by the TF1 flag.

EX1: Enable External Interrupt 1.

This bit sets the masking of External Interrupt 1.

0: Disable external interrupt 1.

1: Enable interrupt requests generated by the /INT1 input.

ET0: Enable Timer 0 Interrupt.

This bit sets the masking of the Timer 0 interrupt.

0: Disable all Timer 0 interrupt.

1: Enable interrupt requests generated by the TF0 flag.

EX0: Enable External Interrupt 0.

This bit sets the masking of External Interrupt 0.

0: Disable external interrupt 0.

1: Enable interrupt requests generated by the /INT0 input.

ESPI0

R/W

Bit6

SFR Definition 12.1. IE: Interrupt Enable

ET2

R/W

Bit5

ES0

R/W

Bit4

Rev. 1.1

ET1

R/W

Bit3

EX1

R/W

Bit2

ET0

R/W

Bit1

SFR Address:

EX0

R/W

Bit0

0xA8

00000000

Addressable

Reset Value

Bit

Related parts for C8051F411EK

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc