A000003 Arduino, A000003 Datasheet - Page 157

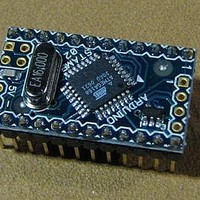

A000003

Manufacturer Part Number

A000003

Description

MCU, MPU & DSP Development Tools MINI

Manufacturer

Arduino

Series

-r

Type

MCUr

Specifications of A000003

Processor To Be Evaluated

Atmega328

Processor Series

ATmega

Data Bus Width

8 bit

Interface Type

USB, RS-232

Operating Supply Voltage

7 V to 9 V

Contents

Board

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

For Use With/related Products

ATmega168

- Current page: 157 of 378

- Download datasheet (8Mb)

17.11.5

17.11.6

17.11.7

2545S–AVR–07/10

OCR2B – Output Compare Register B

TIMSK2 – Timer/Counter2 Interrupt Mask Register

TIFR2 – Timer/Counter2 Interrupt Flag Register

The Output Compare Register A contains an 8-bit value that is continuously compared with the

counter value (TCNT2). A match can be used to generate an Output Compare interrupt, or to

generate a waveform output on the OC2A pin.

The Output Compare Register B contains an 8-bit value that is continuously compared with the

counter value (TCNT2). A match can be used to generate an Output Compare interrupt, or to

generate a waveform output on the OC2B pin.

• Bit 2 – OCIE2B: Timer/Counter2 Output Compare Match B Interrupt Enable

When the OCIE2B bit is written to one and the I-bit in the Status Register is set (one), the

Timer/Counter2 Compare Match B interrupt is enabled. The corresponding interrupt is executed

if a compare match in Timer/Counter2 occurs, that is, when the OCF2B bit is set in the

Timer/Counter 2 Interrupt Flag Register – TIFR2.

• Bit 1 – OCIE2A: Timer/Counter2 Output Compare Match A Interrupt Enable

When the OCIE2A bit is written to one and the I-bit in the Status Register is set (one), the

Timer/Counter2 Compare Match A interrupt is enabled. The corresponding interrupt is executed

if a compare match in Timer/Counter2 occurs, that is, when the OCF2A bit is set in the

Timer/Counter 2 Interrupt Flag Register – TIFR2.

• Bit 0 – TOIE2: Timer/Counter2 Overflow Interrupt Enable

When the TOIE2 bit is written to one and the I-bit in the Status Register is set (one), the

Timer/Counter2 Overflow interrupt is enabled. The corresponding interrupt is executed if an

overflow in Timer/Counter2 occurs, that is, when the TOV2 bit is set in the Timer/Counter2 Inter-

rupt Flag Register – TIFR2.

• Bit 2 – OCF2B: Output Compare Flag 2 B

The OCF2B bit is set (one) when a compare match occurs between the Timer/Counter2 and the

data in OCR2B – Output Compare Register2. OCF2B is cleared by hardware when executing

the corresponding interrupt handling vector. Alternatively, OCF2B is cleared by writing a logic

one to the flag. When the I-bit in SREG, OCIE2B (Timer/Counter2 Compare match Interrupt

Enable), and OCF2B are set (one), the Timer/Counter2 Compare match Interrupt is executed.

Bit

(0xB4)

Read/Write

Initial Value

Bit

(0x70)

Read/Write

Initial Value

Bit

0x17 (0x37)

Read/Write

Initial Value

R/W

R

7

–

0

7

0

R

7

–

0

R/W

R

6

–

0

6

0

R

6

–

0

R

5

–

0

R/W

5

0

R

5

–

0

R

4

–

0

R/W

4

0

R

4

–

0

OCR2B[7:0]

R

3

–

0

R/W

3

0

R

3

–

0

OCIE2B

R/W

OCF2B

2

0

R/W

R/W

ATmega48/88/168

2

0

2

0

OCIE2A

OCF2A

R/W

R/W

R/W

1

0

1

0

1

0

TOIE2

TOV2

R/W

R/W

R/W

0

0

0

0

0

0

TIMSK2

OCR2B

TIFR2

157

Related parts for A000003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO UNO PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO SHIELD PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Development Boards & Kits - AVR ARDUINO STARTER KIT W/ UNO REV3

Manufacturer:

Arduino

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS PROTO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS WITH SD

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Development Software Getting started w/Arduino

Manufacturer:

Arduino

Part Number:

Description:

Ethernet Modules & Development Tools Ethernet Shield for Arduino

Manufacturer:

Arduino

Part Number:

Description:

MCU, MPU & DSP Development Tools LilyPad Arduino Main Board

Manufacturer:

Arduino

Part Number:

Description:

ARDUINO NANO Board

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Ethernet Modules & Development Tools ETHERNET SHEILD PoE FOR ARDUINO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

ATMEGA328 MCU IC W/ Arduino UNO Bootloader

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Memory Cards MICRO SD CARD 1GB WITH SD ADAPTER

Manufacturer:

Arduino