EP1S80B956C7N Altera, EP1S80B956C7N Datasheet - Page 688

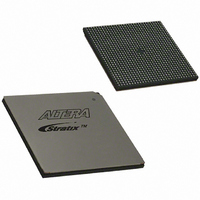

EP1S80B956C7N

Manufacturer Part Number

EP1S80B956C7N

Description

IC STRATIX FPGA 80K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S80B956C7N

Number Of Logic Elements/cells

79040

Number Of Labs/clbs

7904

Total Ram Bits

7427520

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 688 of 864

- Download datasheet (11Mb)

General Architecture

10–4

Stratix Device Handbook, Volume 2

f

Stratix and Stratix GX device MultiTrack interconnect resources are

described in

Direct link routing saves row routing resources while providing fast

communication paths between resource blocks. Direct link interconnects

allow an LAB, digital signal processing (DSP) block, or TriMatrix

memory block to drive data into the local interconnect of its left and right

neighbors. LABs, DSP blocks, and TriMatrix memory blocks can also use

direct link interconnects to drive data back into themselves for feedback.

The Quartus II software automatically uses these routing resources to

enhance design performance.

For more information about LE architecture and the MultiTrack

interconnect structure in Stratix and Stratix GX devices, see the Stratix

Device Family Data Sheet section of the Stratix Device Handbook, Volume 1

or the Stratix GX Device Family Data Sheet section of the Stratix GX Device

Handbook, Volume 1.

DirectDrive Technology

When using APEX II or APE 20K devices, you must place critical paths in

the same MegaLAB

should place critical paths in the same MegaLAB structure for optimal

performance. However, this restriction does not exist in Stratix and

Stratix GX devices because they do not contain MegaLAB structures.

With the new DirectDrive

the actual distance between the source and destination of a path is the

most important criteria for meeting timing performance. DirectDrive

technology ensures that the same routing resources are available to each

design block, regardless of its location in the device.

Row

Row

Row

Row

Column

Column

Column

Routing Type

Table 10–2. Stratix & Stratix GX Device MultiTrack Interconnect Resources

Table

Direct link

R4

R8

R24

C4

C8

C16

Interconnect

10–2.

TM

column to improve performance. Additionally, you

TM

technology in Stratix and Stratix GX devices,

Adjacent LABs and/or blocks

Four LAB units horizontally

Eight LAB units horizontally

Horizontal routing across the width of the device

Four LAB units vertically

Eight LAB units vertically

Vertical routing across the length of the device

Span

Altera Corporation

July 2005

TM

Related parts for EP1S80B956C7N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: