EP1S80B956C7N Altera, EP1S80B956C7N Datasheet - Page 527

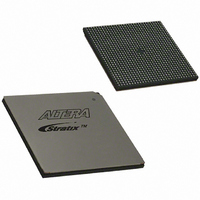

EP1S80B956C7N

Manufacturer Part Number

EP1S80B956C7N

Description

IC STRATIX FPGA 80K LE 956-BGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F484I6N.pdf

(864 pages)

Specifications of EP1S80B956C7N

Number Of Logic Elements/cells

79040

Number Of Labs/clbs

7904

Total Ram Bits

7427520

Number Of I /o

683

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

956-BGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 527 of 864

- Download datasheet (11Mb)

Altera Corporation

July 2005

Notes to

(1)

(2)

(3)

(4)

EP1S25

Table 5–10. EP1S10, EP1S20 & EP1S25 Device Differential Channels (Part 2 of 2)

Device

The first row for each transmitter or receiver reports the number of channels driven directly by the PLL. The second

row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center

PLL. For example, in the 484-pin FineLine BGA EP1S10 device, PLL 1 can drive a maximum of five channels at

840 Mbps or a maximum of 10 channels at 840 Mbps. The Quartus II software may also merge receiver and

transmitter PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum

numbers of receiver and transmitter channels.

The number of channels listed includes the transmitter clock output (tx_outclock) channel. If the design

requires a DDR clock, it can use an extra data channel.

These channels span across two I/O banks per side of the device. When a center PLL clocks channels in the

opposite bank on the same side of the device it is called cross-bank PLL support. Both center PLLs can clock cross-

bank channels simultaneously if, for example, PLL_1 is clocking all RX channels and PLL_2 is clocking all TX

channels. You cannot have two adjacent PLLs simultaneously clocking cross-bank RX channels or two adjacent

PLLs simultaneously clocking TX channels. Cross-bank allows for all receiver channels on one side of the device to

be clocked on one clock while all transmitter channels on the device are clocked on the other center PLL. Crossbank

PLLs are supported at full-speed, 840 Mbps. For wire-bond devices, the full-speed is 624 Mbps.

These values show the channels available for each PLL without crossing another bank.

Table

672-pin FineLine BGA

672-pin BGA

780-pin FineLine BGA Transmitter

1,020-pin FineLine

BGA

5–10:

Package

Transmitter

(2)

Receiver

(2)

Receiver

Transmitter

(2)

Receiver

Transmitter/

Receiver

High-Speed Differential I/O Interfaces in Stratix Devices

Channels

Total

56

58

70

66

78

78

Maximum

(Mbps)

624

624

624

624

840

840

840

840

Speed

840

840

840

840

(4)

(3)

(4)

(3)

(3)

(3)

(3)

(3)

Stratix Device Handbook, Volume 2

PLL 1

14

28

14

29

18

35

17

33

19

39

19

39

Center Fast PLLs

PLL 2

Note (1)

14

28

15

29

17

35

16

33

20

39

20

39

PLL 3

14

28

15

29

17

35

16

33

20

39

20

39

PLL 4

14

28

14

29

18

35

17

33

19

39

19

39

5–55

Related parts for EP1S80B956C7N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 25 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet: