ICS9LPRS525AGILF IDT, Integrated Device Technology Inc, ICS9LPRS525AGILF Datasheet - Page 2

ICS9LPRS525AGILF

Manufacturer Part Number

ICS9LPRS525AGILF

Description

IC CK505 VREG/RES 56TSSOP

Manufacturer

IDT, Integrated Device Technology Inc

Type

Clock Generatorr

Datasheet

1.ICS9LPRS525AFLF.pdf

(21 pages)

Specifications of ICS9LPRS525AGILF

Input

Crystal

Output

Clock

Frequency - Max

400MHz

Voltage - Supply

3.135 V ~ 3.465 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

56-TSSOP

Frequency-max

400MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

800-1932

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ICS9LPRS525AGILF

Manufacturer:

IDT

Quantity:

92

Pin Description

IDT

PIN #

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

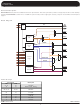

ICS9LPRS525

PC MAIN CLOCK

1

2

3

4

5

6

7

8

9

TM

PC MAIN CLOCK

PCI0/CR#_A

VDDPCI

PCI1/CR#_B

PCI2/TME

PCI3/CFG0

PCI4/SRC5_EN

PCI_F5/ITP_EN

GNDPCI

VDD48

USB_48MHz/FSLA

GND48

VDD96IO

DOTT_96_LRS/SRCT0_LRS

DOTC_96_LRS/SRCC0_LRS

GND

VDD

SRCT1_LRS/SE1

SRCC1_LRS/SE2

GND

VDDPLL3IO

SRCT2_LRS/SATAT_LRS

SRCC2_LRS/SATAC_LRS

GNDSRC

SRCT3_LRS/CR#_C

PIN NAME

TYPE

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

PWR

OUT

OUT

OUT

OUT

OUT

OUT

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

3.3V PCI clock output or Clock Request control A for either SRC0 or SRC2 pair

The power-up default is PCI0 output, but this pin may also be used as a Clock Request control of SRC pair 0 or SRC pair 2 via SMBus. Before

configuring this pin as a Clock Request Pin, the PCI output must first be disabled in byte 2, bit 0 of SMBus address space . After the PCI output is

disabled (high-Z), the pin can then be set to serve as a Clock Request pin for either SRC pair 2 or pair 0 using the CRA#_EN bit located in byte 5 of

SMBUs address space.

Byte 5, bit 7

0 = PCI0 enabled (default)

1= CRA# enabled. Byte 5, bit 6 controls whether CRA# controls SRC0 or SRC2 pair

0 = CRA# controls SRC0 pair (default),

1= CRA# controls SRC2 pair

Power supply for PCI clocks, nominal 3.3V

3.3V PCI clock output/Clock Request control B for either SRC1 or SRC4 pair

The power-up default is PCI1 output, but this pin may also be used as a Clock Request control of SRC pair 1 or SRC pair 4 via SMBus. Before

configuring this pin as a Clock Request Pin, the PCI output must first be disabled in byte 2, bit 1 of SMBus address space . After the PCI output is

disabled (high-Z), the pin can then be set to serve as a Clock Request pin for either SRC pair 1 or pair 4 using the CRB#_EN bit located in byte 5 of

SMBUs address space.

Byte 5, bit 5

0 = PCI1 enabled (default)

1= CRB# enabled. Byte 5, bit 6 controls whether CRB# controls SRC1 or SRC4 pair

Byte 5, bit 4

0 = CRB# controls SRC1 pair (default)

1= CRB# controls SRC4 pair

3.3V PCI clock output / Trusted Mode Enable(TME) Latched Input. This pin is sampled on power-up as follows

0=Overclocking of CPU and SRC allowed

1=Overclocking of CPU and SRC NOT allowed

After being sampled on power-up, this pin becomes a 3.3V PCI Output

3.3V PCI clock output/Configuration Strap. See PCI3 Configuration Table for more information

3.3V PCI clock output / SRC5 pair or PCI_STOP#/CPU_STOP# enable strap. On powerup, the logic value on this pin determines if the SRC5 pair is

enabled or if CPU_STOP#/PCI_STOP# is enabled (pins 29 and 30). The latched value controls the pin function on pins 29 and 30 as follows

0 = PCI_STOP#/CPU_STOP#

1 = SRC5/SRC5#

Free running PCI clock output and ITP/SRC8 enable strap. This output is not affected by the state of the PCI_STOP# pin. On powerup, the state of

this pin determines whether pins 38 and 39 are an ITP or SRC pair.

0 =SRC8/SRC8#

1 = ITP/ITP#

Ground pin for the PCI outputs

Power pin for the 48MHz output and PLL.3.3V

3.3V tolerant input for CPU frequency selection. Refer to input electrical characteristics for Vil_FS and Vih_FS values. / Fixed 48MHz USB clock

output. 3.3V.

Ground pin for the 48MHz outputs

Power supply for DOT96 outputs, 1.05V to 3.3V.

True clock of low power differential SRC or DOT96 with integrated 33 ohm Rs. The power-up default function is SRC0. After powerup, this pin function

may be changed to DOT96 via SMBus Byte 1, bit 7 as follows:

0= SRC0

1=DOT96

Complement clock of low power differential SRC or DOT96 with integrated 33 ohm Rs. The power-up default function is SRC0#. After powerup, this

pin function may be changed to DOT96# via SMBus Byte 1, bit 7 as follows

0= SRC0#

1=DOT96#

Ground pin.

Power supply, nominal 3.3V

True clock of low power differential SRC1 clock pair with integrated 33 ohm Rs. / 3.3V single-ended output. The powerup default is 100 MHz SRC, -

0.5% downspread. The pin function may be changed via SMBus B1b[4:1]

Complement clock of low powerl differential SRC1 clock pair with integrated 33 ohm Rs / 3.3V single-ended output. The powerup default is 100 MHz

SRC, -0.5% downspread. The pin function may be changed via SMBus B1b[4:1]

Ground pin.

Power supply for PLL3 outputs. 1.05V to 3.3V.

True clock of low power differentiall SRC/SATA clock pair with integrated Rs.

Complement clock of low power differential push-pull SRC/SATA clock pair with integrated 33 ohm Rs.

Ground pin for the SRC outputs

True clock of low power differential SRC clock pair with integrated 33 ohm Rs./ Clock Request control C for either SRC0 or SRC2 pair. The power-up

default is SRCCLK3 output, but this pin may also be used as a Clock Request control of SRC pair 0 or SRC pair 2 via SMBus. Before configuring this

pin as a Clock Request Pin, the SRC output must first be disabled in byte 4, bit 7 of SMBus address space . After the SRC output is disabled, the pin

can then be set to serve as a Clock Request pin for either SRC pair 2 or pair 0 using the CRC#_EN bit located in byte 5 of SMBUs address space.

Byte 5, bit 3

0 = SRCCLK3 enabled (default)

1= CRC# enabled. Byte 5, bit 2 controls whether CRC# controls SRC0 or SRC2 pair

0 = CRC# controls SRC0 pair (default),

1= CRC# controls SRC2 pair

Byte 5, bit 6

Byte 5, bit 2

2

DESCRIPTION

1484C—04/20/10