XQ2V1000-4BG575N Xilinx Inc, XQ2V1000-4BG575N Datasheet - Page 22

XQ2V1000-4BG575N

Manufacturer Part Number

XQ2V1000-4BG575N

Description

FPGA 650MHZ CMOS1.5V 575-P

Manufacturer

Xilinx Inc

Series

QPro™ Virtex™-IIr

Datasheet

1.XQ2V1000-4BG575N.pdf

(134 pages)

Specifications of XQ2V1000-4BG575N

Number Of Labs/clbs

1280

Total Ram Bits

737280

Number Of I /o

328

Number Of Gates

100000

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

-55°C ~ 125°C

Package / Case

575-BBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Logic Elements/cells

-

Other names

Q5801737

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

XQ2V1000-4BG575N

Manufacturer:

XILINX

Quantity:

325

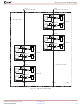

X-Ref Target - Figure 20

X-Ref Target - Figure 21

DS122 (v2.0) December 21, 2007

Product Specification

WCLK

A[3:0]

A[4]

WE

D

DPRA[3:0]

Figure 20: Single-Port Distributed SelectRAM

Figure 21: Dual-Port Distributed SelectRAM

(SR)

(BX)

(BY)

WCLK

A[3:0]

A[3:0]

WE

D

R

4

4

(SR)

(BY)

4

RAM 32x1S

WE0

WE

CK

G[4:1]

WG[4:1]

F[4:1]

WF[4:1]

WSF

WS

WS

WSG

4

4

RAM

(RAM16x1D)

(RAM32x1S)

RAM

RAM 16x1D

DI

DI

D

D

WE

CK

WE

CK

G[4:1]

WG[4:1]

G[4:1]

WG[4:1]

WSG

WSG

WS

WS

F5MUX

dual_port

RAM

dual_port

RAM

DI

DI

D

D

(optional)

D Q

DS031_04_110100

DS031_03_110100

SPO

DPO

Registered

Output

Output

www.xilinx.com

Similar to the RAM configuration, each function generator

(LUT) can implement a 16 x 1-bit ROM. Five configurations

are available: ROM16x1, ROM32x1, ROM64x1,

ROM128x1, and ROM256x1. The ROM elements are

cascadable to implement wider or/and deeper ROM. ROM

contents are loaded at configuration.

number of LUTs occupied by each configuration.

Table 14: ROM Configuration

Shift Registers

Each function generator can also be configured as a 16-bit

shift register. The write operation is synchronous with a clock

input (CLK) and an optional clock enable, as shown in

Figure

bit address bus, A[3:0]. The configurable 16-bit shift register

cannot be set or reset. The read is asynchronous, however, the

storage element or flip-flop is available to implement a

synchronous read. The storage element should always be

used with a constant address. For example, when building an

8-bit shift register and configuring the addresses to point to the

seventh bit, the eighth bit can be the flip-flop. The overall

system performance is improved by using the superior clock-

to-out of the flip-flops.

X-Ref Target - Figure 22

An additional dedicated connection between shift registers

allows connecting the last bit of one shift register to the first

bit of the next, without using the ordinary LUT output. (See

Figure 23, page

dynamic access to any bit in the chain. The shift register

chaining and the MUXF5, MUXF6, and MUXF7 multiplexers

allow up to a 128-bit shift register with addressable access

to be implemented in one CLB.

CE (SR)

D(BY)

A[3:0]

SHIFTIN

CLK

22. A dynamic read access is performed through the 4-

Figure 22: Shift Register Configurations

128 x 1

256 x 1

16 x 1

32 x 1

64 x 1

ROM

4

23.) Longer shift registers can be built with

WE

CK

A[4:1]

WS

SRLC16

WSG

SHIFT-REG

QPro Virtex-II 1.5V Platform FPGAs

MC15

DI

D

SHIFTOUT

Number of LUTs

Table 14

(optional)

D

16 (2 CLBs)

8 (1 CLB)

Q

1

2

4

DS031_05_110600

shows the

Output

Registered

Output

22