PCF8576DT/2,118 NXP Semiconductors, PCF8576DT/2,118 Datasheet - Page 17

PCF8576DT/2,118

Manufacturer Part Number

PCF8576DT/2,118

Description

IC LCD DRIVER 40/160SEG 56TSSOP

Manufacturer

NXP Semiconductors

Datasheet

1.PCF8576DT2118.pdf

(50 pages)

Specifications of PCF8576DT/2,118

Package / Case

56-TSSOP

Display Type

LCD

Configuration

40 Segment

Interface

I²C

Current - Supply

24µA

Voltage - Supply

1.8 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Number Of Digits

20

Number Of Segments

160

Maximum Clock Frequency

400 KHz

Operating Supply Voltage

1.8 V to 5.5 V

Maximum Power Dissipation

400 mW

Maximum Operating Temperature

+ 85 C

Maximum Supply Current

50 mA

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

568-4703 - DEMO BOARD LCD GRAPHIC DRIVER

Digits Or Characters

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

568-3558-2

935276166118

PCF8576DT/2-T

935276166118

PCF8576DT/2-T

NXP Semiconductors

PCF8576D

Product data sheet

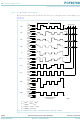

7.10 Display RAM

In the 1:2 multiplex drive mode, BP0 and BP2, BP1 and BP3 all carry the same signals

and may also be paired to increase the drive capabilities.

In the static drive mode the same signal is carried by all four backplane outputs and they

can be connected in parallel for very high drive requirements.

The display RAM is a static 40 × 4-bit RAM which stores LCD data. A logic 1 in the RAM

bit-map indicates the on-state of the corresponding LCD element; similarly, a logic 0

indicates the off-state. There is a one-to-one correspondence between the RAM

addresses and the segment outputs, and between the individual bits of a RAM word and

the backplane outputs. The display RAM bit map

correspond with the backplane outputs BP0 to BP3, and the columns 0 to 39 which

correspond with the segment outputs S0 to S39. In multiplexed LCD applications the

segment data of the first, second, third and fourth row of the display RAM are

time-multiplexed with BP0, BP1, BP2 and BP3 respectively.

When display data is transmitted to the PCF8576D, the display bytes received are stored

in the display RAM in accordance with the selected LCD drive mode. The data is stored as

it arrives and does not wait for an acknowledge cycle as with the commands. Depending

on the current multiplex drive mode, data is stored singularly, in pairs, triplets or

quadruplets. To illustrate the filling order, an example of a 7-segment numeric display

showing all drive modes is given in

applies equally to other LCD types.

Fig 11. Display RAM bit map

backplane outputs

display RAM bits

Display RAM bit map showing direct relationship between RAM addresses and segment outputs;

also between bits in a RAM word and the backplane outputs.

(rows)/

(BP)

All information provided in this document is subject to legal disclaimers.

Rev. 10 — 14 February 2011

0

1

2

3

0

1

2

display RAM addresses (columns)/segment outputs (S)

Figure

3

4

Universal LCD driver for low multiplex rates

12; the RAM filling organization depicted

Figure 11

shows the rows 0 to 3 which

35

PCF8576D

36

© NXP B.V. 2011. All rights reserved.

37

38

mbe525

39

17 of 50