PCF8576DT/2,118 NXP Semiconductors, PCF8576DT/2,118 Datasheet - Page 16

PCF8576DT/2,118

Manufacturer Part Number

PCF8576DT/2,118

Description

IC LCD DRIVER 40/160SEG 56TSSOP

Manufacturer

NXP Semiconductors

Datasheet

1.PCF8576DT2118.pdf

(50 pages)

Specifications of PCF8576DT/2,118

Package / Case

56-TSSOP

Display Type

LCD

Configuration

40 Segment

Interface

I²C

Current - Supply

24µA

Voltage - Supply

1.8 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Number Of Digits

20

Number Of Segments

160

Maximum Clock Frequency

400 KHz

Operating Supply Voltage

1.8 V to 5.5 V

Maximum Power Dissipation

400 mW

Maximum Operating Temperature

+ 85 C

Maximum Supply Current

50 mA

Minimum Operating Temperature

- 40 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

568-4703 - DEMO BOARD LCD GRAPHIC DRIVER

Digits Or Characters

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

568-3558-2

935276166118

PCF8576DT/2-T

935276166118

PCF8576DT/2-T

NXP Semiconductors

PCF8576D

Product data sheet

7.5.1 Internal clock

7.5.2 External clock

7.5 Oscillator

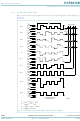

7.6 Timing

7.7 Display register

7.8 Segment outputs

7.9 Backplane outputs

The internal logic of the PCF8576D and its LCD drive signals are timed either by its

internal oscillator or by an external clock. The internal oscillator is enabled by connecting

pin OSC to pin V

as the clock signal for several PCF8576Ds in the system that are connected in cascade.

Pin CLK is enabled as an external clock input by connecting pin OSC to V

The LCD frame signal frequency is determined by the clock frequency (f

Remark: A clock signal must always be supplied to the device; removing the clock may

freeze the LCD in a DC state, which is not suitable for the liquid crystal.

The PCF8576D timing controls the internal data flow of the device. This includes the

transfer of display data from the display RAM to the display segment outputs. In cascaded

applications, the correct timing relationship between each PCF8576D in the system is

maintained by the synchronization signal at pin SYNC. The timing also generates the LCD

frame signal whose frequency is derived from the clock frequency. The frame signal

frequency is a fixed division of the clock frequency from either the internal or an external

clock:

The display latch holds the display data while the corresponding multiplex signals are

generated. There is a one-to-one relationship between the data in the display latch, the

LCD segment outputs and each column of the display RAM.

The LCD drive section includes 40 segment outputs S0 to S39 which should be

connected directly to the LCD. The segment output signals are generated in accordance

with the multiplexed backplane signals and with data residing in the display latch. When

less than 40 segment outputs are required, the unused segment outputs should be left

open-circuit.

The LCD drive section includes four backplane outputs BP0 to BP3 which must be

connected directly to the LCD. The backplane output signals are generated in accordance

with the selected LCD drive mode. If less than four backplane outputs are required, the

unused outputs can be left open-circuit.

In the 1:3 multiplex drive mode, BP3 carries the same signal as BP1, therefore these two

adjacent outputs can be tied together to give enhanced drive capabilities.

f

fr

=

f

-------

24

clk

.

All information provided in this document is subject to legal disclaimers.

SS

. If the internal oscillator is used, the output from pin CLK can be used

Rev. 10 — 14 February 2011

Universal LCD driver for low multiplex rates

PCF8576D

© NXP B.V. 2011. All rights reserved.

clk

DD

).

.

16 of 50