Si5369-EVB Silicon Laboratories Inc, Si5369-EVB Datasheet - Page 80

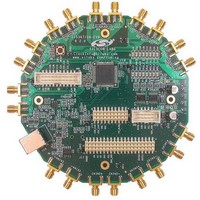

Si5369-EVB

Manufacturer Part Number

Si5369-EVB

Description

MCU, MPU & DSP Development Tools SI5369 DEV KIT

Manufacturer

Silicon Laboratories Inc

Specifications of Si5369-EVB

Processor To Be Evaluated

Si5369

Interface Type

I2C, SPI

Operating Supply Voltage

3.3 V

Lead Free Status / Rohs Status

Details

- Current page: 80 of 84

- Download datasheet (871Kb)

80

Notes:

General

Solder Mask Design

Stencil Design

Card Assembly

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

3. This Land Pattern Design is based on IPC-7351 guidelines.

4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition

5. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder

6. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be

7. The stencil thickness should be 0.125 mm (5 mils).

8. The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.

9. A 4 x 4 array of 0.80 mm square openings on 1.05 mm pitch should be used for the center

10. A No-Clean, Type-3 solder paste is recommended.

11. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for

(LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

mask and the metal pad is to be 60 µm minimum, all the way around the pad.

used to assure good solder paste release.

ground pad.

Small Body Components.

Dimension

GE

GD

ZD

E2

D2

ZE

R1

R2

E

D

X

Y

e

Table 12. PCB Land Pattern Dimensions

Preliminary Rev. 0.4

13.90

13.90

3.90

3.90

MIN

—

—

—

—

15.40 REF.

15.40 REF.

0.50 BSC.

1.50 REF.

0.15 REF

16.90

16.90

MAX

4.10

4.10

0.30

1.00

—

—

Related parts for Si5369-EVB

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc