Si5369-EVB Silicon Laboratories Inc, Si5369-EVB Datasheet - Page 76

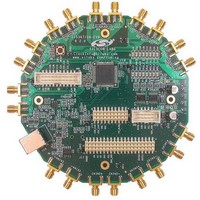

Si5369-EVB

Manufacturer Part Number

Si5369-EVB

Description

MCU, MPU & DSP Development Tools SI5369 DEV KIT

Manufacturer

Silicon Laboratories Inc

Specifications of Si5369-EVB

Processor To Be Evaluated

Si5369

Interface Type

I2C, SPI

Operating Supply Voltage

3.3 V

Lead Free Status / Rohs Status

Details

76

Note: Internal register names are indicated by underlined italics, e.g., INT_PIN. See Si5369 Register Map.

GND PAD

Pin #

77

78

82

83

87

88

90

92

93

97

98

CKOUT3+

CKOUT3–

CKOUT1–

CKOUT1+

CKOUT2+

CKOUT2–

CKOUT4–

CKOUT4+

Pin Name

FS_OUT–

FS_OUT+

GND PAD

CMODE

GND

Table 10. Si5369 Pin Descriptions (Continued)

I/O

O

O

O

O

O

I

Signal Level

LVCMOS

Supply

MULTI

MULTI

MULTI

MULTI

MULTI

Preliminary Rev. 0.4

Clock Output 3.

Differential clock output. Output signal format is selected by

SFOUT3_REG register bits. Output is differential for LVPECL,

LVDS, and CML compatible modes. For CMOS format, both

output pins drive identical single-ended clock outputs.

Clock Output 1.

Differential clock output. Output signal format is selected by

SFOUT1_REG register bits. Output is differential for LVPECL,

LVDS, and CML compatible modes. For CMOS format, both

output pins drive identical single-ended clock outputs.

Frame Sync Output.

Differential frame sync output or fifth high-speed clock output.

Output signal format is selected by SFOUT_FSYNC_REG reg-

ister bits. Output is differential for LVPECL, LVDS, and CML

compatible modes. For CMOS format, both output pins drive

identical single-ended clock outputs. Duty cycle and active

polarity are controlled by FSYNC_PW and FSYNC_POL bits,

respectively. Detailed operations and timing characteristics for

these pins may be found in the Any-Frequency Precision Clock

Family Reference Manual.

Control Mode.

Selects I

0 = I

1 = SPI Control Mode.

This pin must be tied high or low.

Clock Output 2.

Differential clock output. Output signal format is selected by

SFOUT2_REG register bits. Output is differential for LVPECL,

LVDS, and CML compatible modes. For CMOS format, both

output pins drive identical single-ended clock outputs.

Clock Output 4.

Differential clock output. Output signal format is selected by

SFOUT4_REG register bits. Output is differential for LVPECL,

LVDS, and CML compatible modes. For CMOS format, both

output pins drive identical single-ended clock outputs.

Ground Pad.

The ground pad must provide a low thermal and electrical

impedance to a ground plane.

2

C Control Mode.

2

C or SPI control mode for the device.

Description