Si5369-EVB Silicon Laboratories Inc, Si5369-EVB Datasheet - Page 28

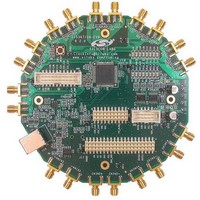

Si5369-EVB

Manufacturer Part Number

Si5369-EVB

Description

MCU, MPU & DSP Development Tools SI5369 DEV KIT

Manufacturer

Silicon Laboratories Inc

Specifications of Si5369-EVB

Processor To Be Evaluated

Si5369

Interface Type

I2C, SPI

Operating Supply Voltage

3.3 V

Lead Free Status / Rohs Status

Details

Reset value = 1110 1101

28

Register 5.

Name

Type

7:6

5:3

2:0

Bit

Bit

SFOUT2_REG [2:0] SFOUT2_REG [2:0]

SFOUT1_REG [2:0] SFOUT1_REG [2:0]

ICMOS [1:0]

D7

ICMOS [1:0]

Name

R/W

D6

ICMOS [1:0].

When the output buffer is set to CMOS mode, these bits determine the output buf-

fer drive strength. The first number below refers to 3.3 V operation; the second to

1.8 V operation. These values assume CKOUT+ is tied to CKOUT-.

00: 8 mA/2 mA

01: 16 mA/4 mA

10: 24 mA/6 mA

11: 32 mA (3.3 V operation)/8mA (1.8 V operation)

Controls output signal format and disable for CKOUT2 output buffer. The LVPECL

and CMOS output formats draw more current than either LVDS or CML; however,

there are restrictions in the allowed output format pin settings so that the maximum

power dissipation for the TQFP devices is limited when they are operated at 3.3 V.

When there are four enabled LVPECL or CMOS outputs, the fifth output must be

disabled. When there are five enabled outputs, there can be no more than three

outputs that are either LVPECL or CMOS.

000: Reserved

001: Disable

010: CMOS

011: Low swing LVDS

100: Reserved

101: LVPECL

110: CML

111: LVDS

Controls output signal format and disable for CKOUT1 output buffer. The LVPECL

and CMOS output formats draw more current than either LVDS or CML; however,

there are restrictions in the allowed output format pin settings so that the maximum

power dissipation for the TQFP devices is limited when they are operated at 3.3 V.

When there are four enabled LVPECL or CMOS outputs, the fifth output must be

disabled. When there are five enabled outputs, there can be no more than three

outputs that are either LVPECL or CMOS.

000: Reserved

001: Disable

010: CMOS

011: Low swing LVDS

100: Reserved

101: LVPECL

110: CML

111: LVDS

D5

SFOUT2_REG [2:0]

Preliminary Rev. 0.4

R/W

D4

D3

Function

D2

SFOUT1_REG [2:0]

R/W

D1

D0