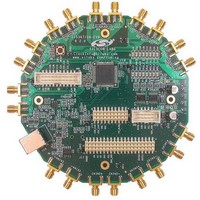

Si5369-EVB Silicon Laboratories Inc, Si5369-EVB Datasheet - Page 61

Si5369-EVB

Manufacturer Part Number

Si5369-EVB

Description

MCU, MPU & DSP Development Tools SI5369 DEV KIT

Manufacturer

Silicon Laboratories Inc

Specifications of Si5369-EVB

Processor To Be Evaluated

Si5369

Interface Type

I2C, SPI

Operating Supply Voltage

3.3 V

Lead Free Status / Rohs Status

Details

Reset value = 0000 0010

Register 132.

Name

Type

7:6

Bit

Bit

5

4

3

2

1

0

FOS4_FLG

FOS3_FLG

FOS2_FLG

FOS1_FLG

LOL_FLG

Reserved

Reserved

Name

D7

R

FOS4_FLG.

CLKIN_4 Frequency Offset Flag.

0: Normal operation.

1: Held version of FOS4_INT. Generates active output interrupt if output interrupt pin is

enabled (INT_PIN=1) and if not masked by FOS4_MSK bit. Flag cleared by writing

location to 0.

FOS3_FLG.

CLKIN_3 Frequency Offset Flag.

0: Normal operation.

1: Held version of FOS3_INT. Generates active output interrupt if output interrupt pin is

enabled (INT_PIN=1) and if not masked by FOS3_MSK bit. Flag cleared by writing

location to 0.

FOS2_FLG.

CLKIN_2 Frequency Offset Flag.

0: Normal operation.

1: Held version of FOS2_INT. Generates active output interrupt if output interrupt pin is

enabled (INT_PIN = 1) and if not masked by FOS2_MSK bit. Flag cleared by writing

location to 0.

FOS1_FLG.

CLKIN_1 Frequency Offset Flag.

0: Normal operation.

1: Held version of FOS1_INT. Generates active output interrupt if output interrupt pin is

enabled (INT_PIN = 1) and if not masked by FOS1_MSK bit. Flag cleared by writing

location to 0.

LOL_FLG.

PLL Loss of Lock Flag.

0: PLL locked

1: Held version of LOL_INT. Generates active output interrupt if output interrupt pin is

enabled (INT_PIN = 1) and if not masked by LOL_MSK bit. Flag cleared by writing

location to 0.

D6

R

FOS4_FLG FOS3_FLG FOS2_FLG FOS1_FLG

R/W

D5

Preliminary Rev. 0.4

R/W

D4

Function

R/W

D3

R/W

D2

LOL_FLG

R/W

D1

D0

R

61