EP1S20F672I7 Altera, EP1S20F672I7 Datasheet - Page 77

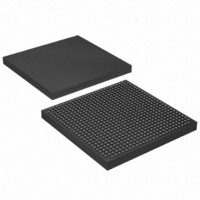

EP1S20F672I7

Manufacturer Part Number

EP1S20F672I7

Description

IC STRATIX FPGA 20K LE 672-FBGA

Manufacturer

Altera

Series

Stratix®r

Datasheet

1.EP1S10F780C7.pdf

(276 pages)

Specifications of EP1S20F672I7

Number Of Logic Elements/cells

18460

Number Of Labs/clbs

1846

Total Ram Bits

1669248

Number Of I /o

426

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

-40°C ~ 100°C

Package / Case

672-FBGA

Family Name

Stratix

Number Of Logic Blocks/elements

18460

# I/os (max)

426

Frequency (max)

420.17MHz

Process Technology

0.13um (CMOS)

Operating Supply Voltage (typ)

1.5V

Logic Cells

18460

Ram Bits

1669248

Operating Supply Voltage (min)

1.425V

Operating Supply Voltage (max)

1.575V

Operating Temp Range

-40C to 100C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

672

Package Type

FBGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Not Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

EP1S20F672I7

Manufacturer:

ALTERA/阿尔特拉

Quantity:

20 000

Company:

Part Number:

EP1S20F672I7N

Manufacturer:

ALTERA20

Quantity:

212

Altera Corporation

July 2005

Adder/Subtractor/Accumulator

The adder/subtractor/accumulator is the first level of the adder/output

block and can be used as an accumulator or as an adder/subtractor.

Adder/Subtractor

Each adder/subtractor/accumulator block can perform addition or

subtraction using the addnsub independent control signal for each first-

level adder in 18 × 18-bit mode. There are two addnsub[1..0] signals

available in a DSP block for any configuration. For 9 × 9-bit mode, one

addnsub[1..0] signal controls the top two one-level adders and

another addnsub[1..0] signal controls the bottom two one-level

adders. A high addnsub signal indicates addition, and a low signal

indicates subtraction. The addnsub control signal can be unregistered or

registered once or twice when feeding the adder blocks to match data

path pipelines.

The signa and signb signals serve the same function as the multiplier

block signa and signb signals. The only difference is that these signals

can be registered up to two times. These signals are tied to the same

signa and signb signals from the multiplier and must be connected to

the same clocks and control signals.

Accumulator

When configured for accumulation, the adder/output block output feeds

back to the accumulator as shown in

accum_sload[1..0] signal synchronously loads the multiplier result

to the accumulator output. This signal can be unregistered or registered

once or twice. Additionally, the overflow signal indicates the

accumulator has overflowed or underflowed in accumulation mode. This

signal is always registered and must be externally latched in LEs if the

design requires a latched overflow signal.

Summation

The output of the adder/subtractor/accumulator block feeds to an

optional summation block. This block sums the outputs of the DSP block

multipliers. In 9 × 9-bit mode, there are two summation blocks providing

the sums of two sets of four 9 × 9-bit multipliers. In 18 × 18-bit mode, there

is one summation providing the sum of one set of four 18 × 18-bit

multipliers.

Figure

Stratix Device Handbook, Volume 1

2–34. The

Stratix Architecture

2–63