EP3C5M164C7N Altera, EP3C5M164C7N Datasheet - Page 51

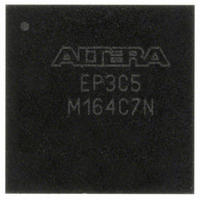

EP3C5M164C7N

Manufacturer Part Number

EP3C5M164C7N

Description

IC CYCLONE III FPGA 5K 164 MBGA

Manufacturer

Altera

Series

Cyclone® IIIr

Datasheets

1.EP3C5F256C8N.pdf

(5 pages)

2.EP3C5F256C8N.pdf

(34 pages)

3.EP3C5F256C8N.pdf

(66 pages)

4.EP3C5F256C8N.pdf

(14 pages)

5.EP3C5F256C8N.pdf

(76 pages)

6.EP3C5M164C7N.pdf

(274 pages)

Specifications of EP3C5M164C7N

Number Of Logic Elements/cells

5136

Number Of Labs/clbs

321

Total Ram Bits

423936

Number Of I /o

106

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

164-MBGA

Family Name

Cyclone III

Number Of Logic Blocks/elements

5136

# I/os (max)

106

Frequency (max)

437.5MHz

Process Technology

65nm

Operating Supply Voltage (typ)

1.2V

Logic Cells

5136

Ram Bits

423936

Operating Supply Voltage (min)

1.15V

Operating Supply Voltage (max)

1.25V

Operating Temp Range

0C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

164

Package Type

MBGA

For Use With

544-2601 - KIT DEV CYCLONE III LS EP3CLS200544-2411 - KIT DEV NIOS II CYCLONE III ED.

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Compliant

Other names

544-2559

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP3C5M164C7N

Manufacturer:

ALTERA

Quantity:

526

- EP3C5F256C8N PDF datasheet

- EP3C5F256C8N PDF datasheet #2

- EP3C5F256C8N PDF datasheet #3

- EP3C5F256C8N PDF datasheet #4

- EP3C5F256C8N PDF datasheet #5

- EP3C5M164C7N PDF datasheet #6

- Current page: 51 of 274

- Download datasheet (6Mb)

Chapter 3: Memory Blocks in the Cyclone III Device Family

Clocking Modes

Clocking Modes

Independent Clock Mode

I/O Clock Mode

© December 2009

1

1

Altera Corporation

Cyclone III device family M9K memory blocks support the following clocking modes:

■

■

■

■

When using read or write clock mode, if you perform a simultaneous read or write to

the same address location, the output read data is unknown. If you require the output

data to be a known value, use either single-clock mode or I/O clock mode and choose

the appropriate read-during-write behavior in the MegaWizard Plug-In Manager.

Violating the setup or hold time on the memory block input registers might corrupt

the memory contents. This applies to both read and write operations.

Asynchronous clears are available on read address registers, output registers, and

output latches only.

Table 3–5

Table 3–5. Cyclone III Device Family Memory Clock Modes

Cyclone III device family M9K memory blocks can implement independent clock

mode for true dual-port memories. In this mode, a separate clock is available for each

port (port A and port B). clock A controls all registers on the port A side, while

clock B controls all registers on the port B side. Each port also supports

independent clock enables for port A and B registers.

Cyclone III device family M9K memory blocks can implement input or output clock

mode for FIFO, single-port, true, and simple dual-port memories. In this mode, an

input clock controls all input registers to the memory block, including data, address,

byteena, wren, and rden registers. An output clock controls the data-output

registers. Each memory block port also supports independent clock enables for input

and output registers.

Independent

Input or output

Read or write

Single-clock

Clocking Mode

Independent

Input or output

Read or write

Single-clock

lists the clocking mode versus memory mode support matrix.

True Dual-Port

Mode

v

v

—

v

Dual-Port

Simple

Mode

v

v

v

—

Single-Port

Mode

—

v

—

v

Cyclone III Device Handbook, Volume 1

ROM Mode

v

v

v

—

FIFO Mode

v

v

—

—

3–15

Related parts for EP3C5M164C7N

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Cyclone III Device Data Sheet

Manufacturer:

ALTERA [Altera Corporation]

Datasheet:

Part Number:

Description:

CYCLONE II STARTER KIT EP2C20N

Manufacturer:

Altera

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 35 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 15 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

CPLD, EP610 Family, ECMOS Process, 300 Gates, 16 Macro Cells, 16 Reg., 16 User I/Os, 5V Supply, 30 Speed Grade, 24DIP

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 7ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Classic EPLD

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

High-performance, low-power erasable programmable logic devices with 8 macrocells, 10ns

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Altera Corporation

Datasheet: