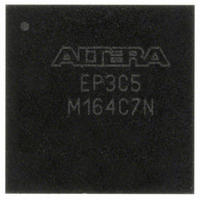

EP3C5M164C7N Altera, EP3C5M164C7N Datasheet - Page 230

EP3C5M164C7N

Manufacturer Part Number

EP3C5M164C7N

Description

IC CYCLONE III FPGA 5K 164 MBGA

Manufacturer

Altera

Series

Cyclone® IIIr

Datasheets

1.EP3C5F256C8N.pdf

(5 pages)

2.EP3C5F256C8N.pdf

(34 pages)

3.EP3C5F256C8N.pdf

(66 pages)

4.EP3C5F256C8N.pdf

(14 pages)

5.EP3C5F256C8N.pdf

(76 pages)

6.EP3C5M164C7N.pdf

(274 pages)

Specifications of EP3C5M164C7N

Number Of Logic Elements/cells

5136

Number Of Labs/clbs

321

Total Ram Bits

423936

Number Of I /o

106

Voltage - Supply

1.15 V ~ 1.25 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

164-MBGA

Family Name

Cyclone III

Number Of Logic Blocks/elements

5136

# I/os (max)

106

Frequency (max)

437.5MHz

Process Technology

65nm

Operating Supply Voltage (typ)

1.2V

Logic Cells

5136

Ram Bits

423936

Operating Supply Voltage (min)

1.15V

Operating Supply Voltage (max)

1.25V

Operating Temp Range

0C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

164

Package Type

MBGA

For Use With

544-2601 - KIT DEV CYCLONE III LS EP3CLS200544-2411 - KIT DEV NIOS II CYCLONE III ED.

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Compliant

Other names

544-2559

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP3C5M164C7N

Manufacturer:

ALTERA

Quantity:

526

9–70

Table 9–22. Dedicated Configuration Pins on Cyclone III Device Family (Part 3 of 4)

Cyclone III Device Handbook, Volume 1

DCLK

DATA[0]

DATA[1],

ASDO

Pin Name

Mode

User

N/A

I/O

I/O

Chapter 9: Configuration, Design Security, and Remote System Upgrades in the Cyclone III Device Family

Configuration

PS, FPP, AS,

PS, FPP, AS,

FPP, AS, AP

Scheme

AP

AP

(1)

(1)

(1)

FPP). Output

Output (AS).

Bidirectional

Bidirectional

Input (FPP),

(AS, AP(1))

Input (PS,

Input (PS,

FPP, AS).

Pin Type

(AP)

(AP)(1)

(1)

In PS and FPP configuration, DCLK is the clock input used to

clock data from an external source into the target Cyclone III

device family. Data is latched into the device on the rising

edge of DCLK.

In AS mode, DCLK is an output from the Cyclone III device

family that provides timing for the configuration interface, it

has an internal pull-up resistor (typically 25 kΩ) that is

always active.

In AP mode,

that provides timing for the configuration interface.

In active configuration schemes (AS or AP), this pin will be

driven into an inactive state after configuration completes.

Alternatively, in active schemes, you can use this pin as a

user I/O during user mode. In passive schemes (PS or FPP)

that use a control host, DCLK must be driven either high or

low, whichever is more convenient. In passive schemes, you

cannot use DCLK as a user I/O in user mode. Toggling this

pin after configuration does not affect the configured device

Data input. In serial configuration modes, bit-wide

configuration data is presented to the target Cyclone III

device family on the DATA[0] pin.

In AS mode, DATA[0] has an internal pull-up resistor that is

always active. After AS configuration, DATA[0] is a

dedicated input pin with optional user control.

After PS or FPP configuration, DATA[0] is available as a

user I/O pin and the state of this pin depends on the

Dual-Purpose Pin settings.

After AP configuration, DATA[0] is a dedicated bidirectional

pin with optional user control.

Data input in non-AS mode. Control signal from the

Cyclone III device family to the serial configuration device in

AS mode used to read out configuration data. The DATA[1]

pin functions as the ASDO pin in AS mode.

In AS mode, DATA[1] has an internal pull-up resistor that is

always active. After AS configuration, DATA[1] is a

dedicated output pin with optional user control.

In PS configuration scheme, DATA[1] functions as user I/O

pin during configuration, which means it is tri-stated.

After FPP configuration, DATA[1] is available as a user I/O

pin and the state of this pin depends on the Dual-Purpose

Pin settings.

In AP configuration scheme, which is for Cyclone III devices

only, the byte-wide or word-wide configuration data is

presented to the target Cyclone III device on DATA[7..0]

or DATA[15..0], respectively. After AP configuration,

DATA[1] is a dedicated bidirectional pin with optional user

control.

(1)

DCLK is an output from the Cyclone III device

Description

© December 2009 Altera Corporation

(1)

Configuration Features

(1)