ATSAM3S4CA-CU Atmel, ATSAM3S4CA-CU Datasheet - Page 453

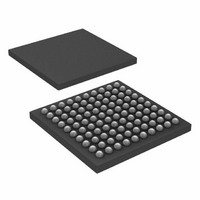

ATSAM3S4CA-CU

Manufacturer Part Number

ATSAM3S4CA-CU

Description

IC MCU 32BIT 256KB FLASH 100BGA

Manufacturer

Atmel

Series

SAM3Sr

Specifications of ATSAM3S4CA-CU

Core Processor

ARM® Cortex-M3™

Core Size

32-Bit

Speed

64MHz

Connectivity

EBI/EMI, I²C, MMC, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, I²S, POR, PWM, WDT

Number Of I /o

79

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

48K x 8

Voltage - Supply (vcc/vdd)

1.62 V ~ 1.95 V

Data Converters

A/D 16x10/12b, D/A 2x12b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-LFBGA

Processor Series

ATSAM3x

Core

ARM Cortex M3

3rd Party Development Tools

JTRACE-CM3, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

ATSAM3S-EK

Package

100LFBGA

Device Core

ARM Cortex M3

Family Name

AT91

Maximum Speed

64 MHz

Operating Supply Voltage

1.8|3.3 V

Data Bus Width

32 Bit

Number Of Programmable I/os

79

Interface Type

I2C/I2S/SPI/UART/USART/USB

On-chip Adc

16-chx12-bit

On-chip Dac

2-chx12-bit

Number Of Timers

6

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATSAM3S4CA-CU

Manufacturer:

SANYO

Quantity:

1 000

- Current page: 453 of 1118

- Download datasheet (24Mb)

26.16.9

Name:

Address:

Access:

Possible limitations on PLLA input frequencies and multiplier factors should be checked before using the PMC.

Warning: Bit 29 must always be set to 1 when programming the CKGR_PLLAR register.

This register can only be written if the WPEN bit is cleared in

• DIVA: Divider

• PLLACOUNT: PLLA Counter

Specifies the number of Slow Clock cycles x8 before the LOCKA bit is set in PMC_SR after CKGR_PLLAR is written.

• MULA: PLLA Multiplier

0 = The PLLA is deactivated.

1 up to 2047 = The PLLA Clock frequency is the PLLA input frequency multiplied by MULA + 1.

6500C–ATARM–8-Feb-11

DIVA

0

1

2 - 255

31

23

15

–

–

7

PMC Clock Generator PLLA Register

CKGR_PLLAR

0x400E0428

Read-write

30

22

14

–

–

6

29

21

13

1

5

Divider Selected

Divider output is 0

Divider is bypassed (DIVA=1)

Divider output is DIVA

28

20

12

–

4

MULA

DIVA

“PMC Write Protect Mode Register” on page

27

19

11

–

3

PLLACOUNT

26

18

10

2

SAM3S Preliminary

MULA

25

17

9

1

466.

24

16

8

0

453

Related parts for ATSAM3S4CA-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR ATSAM3S4C

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

Development Boards & Kits - ARM EVAL KIT SAM3S8 & SAM3SD8 series

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

AT91 ARM Cortex M3-based Processor

Manufacturer:

ATMEL [ATMEL Corporation]

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet: