ATSAM3S4CA-CU Atmel, ATSAM3S4CA-CU Datasheet - Page 366

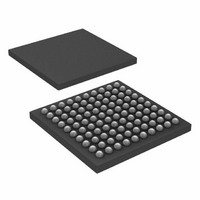

ATSAM3S4CA-CU

Manufacturer Part Number

ATSAM3S4CA-CU

Description

IC MCU 32BIT 256KB FLASH 100BGA

Manufacturer

Atmel

Series

SAM3Sr

Specifications of ATSAM3S4CA-CU

Core Processor

ARM® Cortex-M3™

Core Size

32-Bit

Speed

64MHz

Connectivity

EBI/EMI, I²C, MMC, SPI, SSC, UART/USART, USB

Peripherals

Brown-out Detect/Reset, DMA, I²S, POR, PWM, WDT

Number Of I /o

79

Program Memory Size

256KB (256K x 8)

Program Memory Type

FLASH

Ram Size

48K x 8

Voltage - Supply (vcc/vdd)

1.62 V ~ 1.95 V

Data Converters

A/D 16x10/12b, D/A 2x12b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

100-LFBGA

Processor Series

ATSAM3x

Core

ARM Cortex M3

3rd Party Development Tools

JTRACE-CM3, MDK-ARM, RL-ARM, ULINK2

Development Tools By Supplier

ATSAM3S-EK

Package

100LFBGA

Device Core

ARM Cortex M3

Family Name

AT91

Maximum Speed

64 MHz

Operating Supply Voltage

1.8|3.3 V

Data Bus Width

32 Bit

Number Of Programmable I/os

79

Interface Type

I2C/I2S/SPI/UART/USART/USB

On-chip Adc

16-chx12-bit

On-chip Dac

2-chx12-bit

Number Of Timers

6

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATSAM3S4CA-CU

Manufacturer:

SANYO

Quantity:

1 000

- Current page: 366 of 1118

- Download datasheet (24Mb)

23.7

23.7.1

23.7.1.1

23.7.1.2

23.7.1.3

366

Application Example

SAM3S Preliminary

Implementation Examples

8-bit NAND Flash

Hardware Configuration

Software Configuration

Hardware configurations are given for illustration only. The user should refer to the manufacturer

web site to check for memory device availability.

For Hardware implementation examples, please refer to ATSAM3S-EK schematics, which show

examples of a connection to an LCD module and NAND Flash.

Perform the following configuration:

In this example, the NAND Flash is not addressed as a “CE don’t care”. To address it as a “CE

don’t care”, connect NCS3 (if SMC_NFCS3 is set) to the NAND Flash CE.

• Assign the SMC_NFCSx (for example SMC_NFCS3) field in the CCFG_SMCNFCS Register

• Reserve A21 / A22 for ALE / CLE functions. Address and Command Latches are controlled

• NANDOE and NANDWE signals are multiplexed with PIO lines. Thus, the dedicated PIOs

• Configure a PIO line as an input to manage the Ready/Busy signal.

• Configure Static Memory Controller CS3 Setup, Pulse, Cycle and Mode according to NAND

(ANY PIO)

NANDOE

NANDWE

(ANY PIO)

on the Bus Matrix User Interface.

respectively by setting to 1 the address bits A21 and A22 during accesses.

must be programmed in peripheral mode in the PIO controller.

Flash timings, the data bus width and the system bus frequency.

D[0..7]

CLE

ALE

3V3

R1

R1

R2

R2

10K

10K

10K

10K

16

17

18

19

10

11

14

15

20

21

22

23

24

25

26

8

9

7

1

2

3

4

5

6

U1

U1

CLE

ALE

RE

WE

CE

R/B

WP

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

TSOP48 PACKAGE

2 Gb

K9F2G08U0M

K9F2G08U0M

PRE

VCC

VCC

VSS

VSS

I/O0

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

N.C

29

30

31

32

41

42

43

44

48

47

46

45

40

39

38

35

34

33

28

27

37

12

36

13

D0

D1

D2

D3

D4

D5

D6

D7

C1

C1

100NF

100NF

3V3

C2

C2

100NF

100NF

6500C–ATARM–8-Feb-11

Related parts for ATSAM3S4CA-CU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT EVAL FOR ATSAM3S4C

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

Development Boards & Kits - ARM EVAL KIT SAM3S8 & SAM3SD8 series

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

AT91 ARM Cortex M3-based Processor

Manufacturer:

ATMEL [ATMEL Corporation]

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet: