AT89C51ID2-RLTUM Atmel, AT89C51ID2-RLTUM Datasheet - Page 111

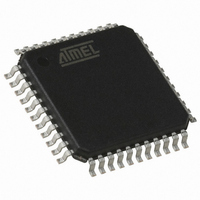

AT89C51ID2-RLTUM

Manufacturer Part Number

AT89C51ID2-RLTUM

Description

IC 8051 MCU FLASH 64K 44VQFP

Manufacturer

Atmel

Series

89Cr

Datasheet

1.AT89C51ID2-RLTUM.pdf

(157 pages)

Specifications of AT89C51ID2-RLTUM

Core Processor

8051

Core Size

8-Bit

Speed

60MHz

Connectivity

I²C, SPI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

34

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Eeprom Size

2K x 8

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

44-TQFP, 44-VQFP

Processor Series

AT89x

Core

8051

Data Bus Width

8 bit

Data Ram Size

2 KB

Interface Type

UART, SPI, TWI

Maximum Clock Frequency

60 MHz

Number Of Programmable I/os

34

Number Of Timers

3

Operating Supply Voltage

2.7 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Minimum Operating Temperature

- 40 C

Package

44VQFP

Device Core

8051

Family Name

89C

Maximum Speed

40 MHz

Height

1.45 mm

Length

10.1 mm

Supply Voltage (max)

5.5 V

Supply Voltage (min)

2.7 V

Width

10.1 mm

For Use With

AT89OCD-01 - USB EMULATOR FOR AT8XC51 MCU

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Data Converters

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89C51ID2-RLTUM

Manufacturer:

ATMEL

Quantity:

13 937

EEPROM Data

Memory

Write Data

4289C–8051–11/05

The 2K bytes on-chip EEPROM memory block is located at addresses 0000h to 07FFh

of the XRAM/ERAM memory space and is selected by setting control bits in the EECON

register.

A read or write access to the EEPROM memory is done with a MOVX instruction.

Data is written by byte to the EEPROM memory block as for an external RAM memory.

The following procedure is used to write to the EEPROM memory:

•

•

•

•

•

•

•

•

•

•

Figure 43 represents the optimal write sequence to the on-chip EEPROM data memory.

Check EEBUSY flag

If the user application interrupts routines use XRAM memory space: Save and

disable interrupts.

Load DPTR with the address to write

Store A register with the data to be written

Set bit EEE of EECON register

Execute a MOVX @DPTR, A

Clear bit EEE of EECON register

Restore interrupts.

EEBUSY flag in EECON is then set by hardware to indicate that programming is in

progress and that the EEPROM segment is not available for reading or writing.

The end of programming is indicated by a hardware clear of the EEBUSY flag.

AT89C51ID2

111