SX1211I084TRT Semtech, SX1211I084TRT Datasheet - Page 61

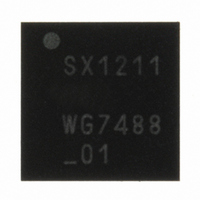

SX1211I084TRT

Manufacturer Part Number

SX1211I084TRT

Description

IC SNGL-CHIP TXRX 32-TQFN

Manufacturer

Semtech

Specifications of SX1211I084TRT

Frequency

860 ~ 960MHz

Data Rate - Maximum

200kbps

Modulation Or Protocol

FSK, OOK

Applications

AMR, ISM, Security and Access

Power - Output

12.5dBm

Sensitivity

-113dBm

Voltage - Supply

2.1 V ~ 3.6 V

Current - Receiving

3mA

Current - Transmitting

25mA

Data Interface

PCB, Surface Mount

Antenna Connector

PCB, Surface Mount

Operating Temperature

-40°C ~ 85°C

Package / Case

32-TQFN

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Operating Temperature Classification

Industrial

Modulation Type

FSK/OOK

Package Type

TQFN EP

Operating Supply Voltage (min)

2.1V

Operating Supply Voltage (typ)

2.5/3.3V

Operating Supply Voltage (max)

3.6V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Memory Size

-

Lead Free Status / Rohs Status

Compliant

Other names

SX1211I084TRT

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

SX1211I084TRT

Manufacturer:

HITTITE

Quantity:

560

Rev 7 – Sept 2

ADVANCED COMMUNICATIONS & SENSING

Fifo_fill

Tx_done

Tx_start_irq_0

Res

RSSI_irq

PLL_locked

PLL_lock_en

RSSI_irq_thresh

nd

, 2008

6

5

4

3

2

1

0

7-0

14

14

14

14

14

14

14

15

r/w/

c

r

r/w

r/w

r/w/

c

r/w/

c

r/w

0

1

FIFO filling status/control (Buffered mode only):

Goes high when FIFO is being filled (sync word has been detected)

Writing ‘1’ clears the bit and waits for a new sync word (if Fifo_overrun_clr=0)

0

1

Tx_done IRQ source

Goes high when the last bit has left the shift register.

Tx start condition and IRQ_0 source:

0

1

0

equal to the threshold set by MCParam_Fifo_thresh parameter (Cf section

5.2.2.3), IRQ_0 mapped to Fifo_threshold (d)

1

(d): “0”, should be set to “1”.

Note: “0” disables the RSSI IRQ source. It can be left enabled at any time, and

the user can choose to map this interrupt to IRQ0/IRQ1 or not.

RSSI IRQ source:

Goes high when a signal above RSSI_irq_thresh is detected

Writing ‘1’ clears the bit

PLL status:

0

1

Writing a ‘1’ clears the bit

PLL_lock detect flag mapped to pin 23:

0

1

RSSI threshold for interrupt (coded as RSSI)

(d): “00000000”

If Fifo_fill_method = ‘0’: (d)

If Fifo_fill_method = ‘1’:

If Data_mode(1:0) = 01 (Buffered mode):

If Data_mode(1:0) = 1x (Packet mode):

Automatically starts when a sync word is detected (d)

Manually controlled by Fifo_fill

Stop filling the FIFO

Start filling the FIFO

Tx starts if FIFO is full, IRQ_0 mapped to /Fifoempty (d)

Tx starts if FIFO is not empty, IRQ_0 mapped to /Fifoempty

Tx starts if FIFO is not empty, IRQ_0 mapped to /Fifoempty

not locked

locked

Lock detect disabled, pin 23 is High-Z

Lock detect enabled(d)

Start transmission when the number of bytes in FIFO is greater than or

Page 61 of 92

www.semtech.com

SX1211