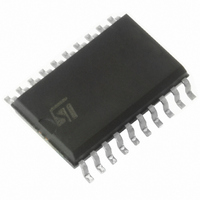

ST72F623F2M1 STMicroelectronics, ST72F623F2M1 Datasheet - Page 69

ST72F623F2M1

Manufacturer Part Number

ST72F623F2M1

Description

IC MCU 8BIT LS 8K 20-SOIC

Manufacturer

STMicroelectronics

Series

ST7r

Datasheet

1.ST72F622L2M1.pdf

(139 pages)

Specifications of ST72F623F2M1

Core Processor

ST7

Core Size

8-Bit

Speed

8MHz

Connectivity

USB

Peripherals

DMA, LVD, POR, PWM, WDT

Number Of I /o

11

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Ram Size

384 x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 3x10b

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

20-SOIC (7.5mm Width)

Processor Series

ST72F6x

Core

ST7

Data Bus Width

8 bit

Data Ram Size

384 B

Interface Type

SCI, SPI, USB

Maximum Clock Frequency

12 MHz

Number Of Programmable I/os

11

Number Of Timers

2

Operating Supply Voltage

4 V to 5.5 V

Maximum Operating Temperature

+ 70 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

0 C

On-chip Adc

10 bit

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

497-2114-5

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST72F623F2M1

Manufacturer:

NXP

Quantity:

670

Part Number:

ST72F623F2M1

Manufacturer:

ST

Quantity:

20 000

SERIAL COMMUNICATIONS INTERFACE (Cont’d)

10.5.4 Functional Description

The block diagram of the Serial Control Interface,

is shown in

isters:

– Two control registers (SCICR1 & SCICR2)

– A status register (SCISR)

– A baud rate register (SCIBRR)

– An extended prescaler receiver register (SCIER-

– An extended prescaler transmitter register (SCI-

Refer to the register descriptions in

10.5.7for the definitions of each bit.

Figure 47. Word Length Programming

PR)

ETPR)

9-bit Word length (M bit is set)

Start

Figure 46

Bit

8-bit Word length (M bit is reset)

Start

Bit

Bit0

Bit0

It contains six dedicated reg-

Bit1

Bit1

Break Frame

Data Frame

Idle Frame

Break Frame

Data Frame

Idle Frame

Bit2

Bit2

Bit3

Bit3

Section

Bit4

Bit4

Doc ID 6996 Rev 5

Bit5

Bit5

10.5.4.1 Serial Data Format

Word length may be selected as being either 8 or 9

bits by programming the M bit in the SCICR1 reg-

ister (see

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as an entire frame

of “1”s followed by the start bit of the next frame

which contains data.

A Break character is interpreted on receiving “0”s

for some multiple of the frame period. At the end of

the last break frame the transmitter inserts an ex-

tra “1” bit to acknowledge the start bit.

Transmission and reception are driven by their

own baud rate generator.

Bit6

Bit6

Possible

Bit7

Parity

Figure

Bit7

Bit

Possible

Parity

Bit8

Bit

Stop

Bit

46).

Stop

Bit

Extra

Start

Next

Start

Bit

Bit

‘1’

Extra

Next Data Frame

Next

Start

Start

Bit

Bit

‘1’

Start

Bit

Next Data Frame

Start

Bit

ST7262xxx

69/139