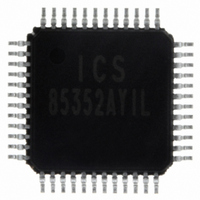

ICS85352AYILF IDT, Integrated Device Technology Inc, ICS85352AYILF Datasheet - Page 9

ICS85352AYILF

Manufacturer Part Number

ICS85352AYILF

Description

IC CLK MUX 2:1 LVPECL 48-TQFP

Manufacturer

IDT, Integrated Device Technology Inc

Series

HiPerClockS™r

Type

Multiplexerr

Datasheet

1.ICS85352AYILF.pdf

(20 pages)

Specifications of ICS85352AYILF

Number Of Circuits

1

Ratio - Input:output

2:12

Differential - Input:output

Yes/Yes

Input

HCSL, LVDS, LVHSTL, LVPECL, SSTL

Output

LVPECL

Frequency - Max

700MHz

Voltage - Supply

3.135 V ~ 3.465 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

48-TQFP, 48-VQFP

Frequency-max

700MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

800-1174

85352AYILF

85352AYILF

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ICS85352AYILF

Manufacturer:

IDT, Integrated Device Technology Inc

Quantity:

10 000

Company:

Part Number:

ICS85352AYILFT

Manufacturer:

IDT, Integrated Device Technology Inc

Quantity:

10 000

ICS85352I Data Sheet

EPAD Thermal Release Path

In order to maximize both the removal of heat from the package and

the electrical performance, a land pattern must be incorporated on

the Printed Circuit Board (PCB) within the footprint of the package

corresponding to the exposed metal pad or exposed heat slug on the

package, as shown in Figure 2. The solderable area on the PCB, as

defined by the solder mask, should be at least the same size/shape

as the exposed pad/slug area on the package to maximize the

thermal/electrical performance. Sufficient clearance should be

designed on the PCB between the outer edges of the land pattern

and the inner edges of pad pattern for the leads to avoid any shorts.

While the land pattern on the PCB provides a means of heat transfer

and electrical grounding from the package to the board through a

solder joint, thermal vias are necessary to effectively conduct from

the surface of the PCB to the ground plane(s). The land pattern must

be connected to ground through these vias. The vias act as “heat

pipes”. The number of vias (i.e. “heat pipes”) are application specific

Figure 2. Assembly for Exposed Pad Thermal Release Path - Side View (drawing not to scale)

ICS85352AYI REVISION C AUGUST 3, 2010

SOLDER

PIN PAD

PIN

GROUND PLANE

EXPOSED HEAT SLUG

THERMAL VIA

9

and dependent upon the package power dissipation as well as

electrical conductivity requirements. Thus, thermal and electrical

analysis and/or testing are recommended to determine the minimum

number needed. Maximum thermal and electrical performance is

achieved when an array of vias is incorporated in the land pattern. It

is recommended to use as many vias connected to ground as

possible. It is also recommended that the via diameter should be 12

to 13mils (0.30 to 0.33mm) with 1oz copper via barrel plating. This is

desirable to avoid any solder wicking inside the via during the

soldering process which may result in voids in solder between the

exposed pad/slug and the thermal land. Precautions should be taken

to eliminate any solder voids between the exposed heat slug and the

land pattern. Note: These recommendations are to be used as a

guideline only. For further information, refer to the Application Note

on the Surface Mount Assembly of Amkor’s Thermally/Electrically

Enhance Leadframe Base Package, Amkor Technology.

LAND PATTERN

(GROUND PAD)

SOLDER

12 BIT, 2-TO-1, 3.3V, 2.5V LVPECL CLOCK BUFFER

PIN

©2010 Integrated Device Technology, Inc.

PIN PAD

SOLDER