CY7C60223-PXC Cypress Semiconductor Corp, CY7C60223-PXC Datasheet - Page 58

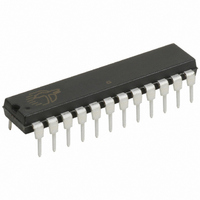

CY7C60223-PXC

Manufacturer Part Number

CY7C60223-PXC

Description

IC MCU 8K WIRELESS 24-DIP

Manufacturer

Cypress Semiconductor Corp

Series

enCoRe™ II CY7C602xxr

Datasheet

1.CY7C60123-PVXC.pdf

(68 pages)

Specifications of CY7C60223-PXC

Core Processor

M8C

Core Size

8-Bit

Speed

12MHz

Connectivity

SPI

Peripherals

LVD, POR, WDT

Number Of I /o

20

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

24-DIP (0.300", 7.62mm)

For Use With

770-1001 - ISP 4PORT CYPRESS ENCORE II MCUCY3216 - KIT PROGRAMMER MODULAR428-1774 - EXTENSION KIT FOR ENCORE II428-1773 - KIT DEVELOPMENT ENCORE II

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Other names

428-1797

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY7C60223-PXC

Manufacturer:

TEXAS

Quantity:

93

Table 19-6. Interrupt Mask 1 (INT_MSK1) [0xE1] [R/W]

Table 19-7. Interrupt Mask 0 (INT_MSK0) [0xE0] [R/W]

19.4.3 Interrupt Vector Clear Register

Table 19-8. Interrupt Vector Clear Register (INT_VC) [0xE2] [R/W]

Document 38-16016 Rev. *F

Bit 7: TCAP0 Interrupt Enable

0 = Mask TCAP0 interrupt

1 = Unmask TCAP0 interrupt

Bit 6: Prog Interval Timer Interrupt Enable

0 = Mask Prog Interval Timer interrupt

1 = Unmask Prog Interval Timer interrupt

Bit 5: 1 ms Timer Interrupt Enable

0 = Mask 1 ms interrupt

1 = Unmask 1 ms interrupt

Bit [4:0]: Reserved

Bit 7: GPIO Port 1 Interrupt Enable

0 = Mask GPIO Port 1 interrupt

1 = Unmask GPIO Port 1 interrupt

Bit 6: Sleep Timer Interrupt Enable

0 = Mask Sleep Timer interrupt

1 = Unmask Sleep Timer interrupt

Bit 5: INT1 Interrupt Enable

0 = Mask INT1 interrupt

1 = Unmask INT1 interrupt

Bit 4: GPIO Port 0 Interrupt Enable

0 = Mask GPIO Port 0 interrupt

1 = Unmask GPIO Port 0 interrupt

Bit 3: SPI Receive Interrupt Enable

0 = Mask SPI Receive interrupt

1 = Unmask SPI Receive interrupt

Bit 2: SPI Transmit Enable

0 = Mask SPI Transmit interrupt

1 = Unmask SPI Transmit interrupt

Bit 1: INT0 Interrupt Enable

0 = Mask INT0 interrupt

1 = Unmask INT0 interrupt

Bit 0: POR/LVD Interrupt Enable

0 = Mask POR/LVD interrupt

1 = Unmask POR/LVD interrupt

The Interrupt Vector Clear Register (INT_VC) holds the interrupt vector for the highest priority pending interrupt when read, and when

written clears all pending interrupts.

Bit [7:0]: Pending Interrupt [7:0]

8-bit data value holds the interrupt vector for the highest priority pending interrupt. Writing to this register clears all pending interrupts.

Read/Write

Read/Write

Read/Write

Default

Default

Default

Field

Field

Field

Bit #

Bit #

Bit #

GPIO Port 1

Int Enable

Int Enable

TCAP0

R/W

R/W

R/W

7

0

7

0

7

0

Prog Interval

Sleep Timer

Int Enable

Int Enable

Timer

R/W

R/W

R/W

6

0

6

0

6

0

1-ms Timer

Int Enable

Int Enable

INT1

R/W

R/W

R/W

5

0

5

0

5

0

GPIO Port 0

Int Enable

R/W

Pending Interrupt [7:0]

R/W

4

–

0

4

0

4

0

SPI Receive

Int Enable

R/W

R/W

3

–

0

3

0

3

0

SPI Transmit

Int Enable

Reserved

R/W

R/W

CY7C601xx, CY7C602xx

2

–

0

2

0

2

0

Int Enable

INT0

R/W

R/W

1

–

0

1

0

1

0

Int Enable

POR/LVD

Page 58 of 68

R/W

R/W

0

–

0

0

0

0

0

[+] Feedback