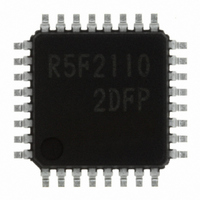

R5F21102DFP#U0 Renesas Electronics America, R5F21102DFP#U0 Datasheet - Page 116

R5F21102DFP#U0

Manufacturer Part Number

R5F21102DFP#U0

Description

IC R8C MCU FLASH 8K 32LQFP

Manufacturer

Renesas Electronics America

Series

M16C™ M16C/R8C/Tiny/10r

Datasheets

1.R5F211A2SPU0.pdf

(300 pages)

2.R5F21102FPU0.pdf

(30 pages)

3.R5F21102FPU0.pdf

(201 pages)

Specifications of R5F21102DFP#U0

Core Processor

R8C

Core Size

16-Bit

Speed

16MHz

Connectivity

SIO, UART/USART

Peripherals

LED, WDT

Number Of I /o

22

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-LQFP

For Use With

R0K521134S000BE - KIT EVAL STARTER FOR R8C/13R0E521134EPB00 - KIT EMULATOR PROBE FOR PC7501R0E521134CPE00 - EMULATOR COMPACT R8C/13

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

- Current page: 116 of 201

- Download datasheet (2Mb)

R8C/10 Group

Rev.1.20 Jan 27, 2006

REJ09B0019-0120

14. A/D Converter

NOTES:

1. Does not depend on use of sample and hold function.

2. The frequency of

3. In repeat mode, only 8-bit mode can be used.

Table 14.1 Performance of A/D converter

Method of A/D conversion Successive approximation (capacitive coupling amplifier)

Analog input voltage

Operating clock

Resolution

Integral nonlinearity error

Operating modes

Analog input pins

A/D conversion start condition ADST bit in ADCON0 register is set to “1” (A/D conversion starts)

Conversion speed per pin • Without sample and hold function

The A/D converter consists of one 10-bit successive approximation A/D converter circuit with a capacitive

coupling amplifier. The analog inputs share the pins with P0

make sure the corresponding port direction bits are set to “0” (input mode).

When not using the A/D converter, set the VCUT bit to “0” (Vref unconnected), so that no current will flow

from the V

The result of A/D conversion is stored in the AD register.

Table 14.1 shows the performance of the A/D converter. Figure 14.1 shows a block diagram of the A/D

converter, and Figures 14.2 and 14.3 show the A/D converter-related registers.

When AVcc is less than 4.2V,

Without sample and hold function, the

With the sample and hold function, the

Item

REF

pin into the resistor ladder, helping to reduce the power consumption of the chip.

AD (2)

page 104 of 180

AD

(1)

must be 10 MHz or less.

0V to Vref

AV

AV

8-bit or 10-bit (selectable)

AV

• 8-bit resolution ±2LSB

• 10-bit resolution ±3LSB

AVcc = Vref = 3.3V

• 8-bit resolution ±2LSB

• 10-bit resolution ±5LSB

One-shot mode and repeat mode

8 pins (AN

• With sample and hold function

8-bit resolution: 49

8-bit resolution: 28

CC

CC

CC

AD

= 5V f

= 3V divide-by-2 of f

= Vref = 5V

must be f

0

to AN

AD

AD

AD

, divide-by-2 of f

frequency should be 250 kHz or more.

7

frequency should be 1 MHz or more.

AD

)

/2 or less by dividing f

AD

AD

cycles, 10-bit resolution: 59

cycles, 10-bit resolution: 33

AD

, divide-by-4 of f

Performance

AD

(3)

0

, divide-by-4 of f

to P0

7

. Therefore, when using these pins,

AD

.

AD

AD

AD

AD

cycles

cycles

14. A/D Converter

Related parts for R5F21102DFP#U0

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: