C8051F988-GM Silicon Laboratories Inc, C8051F988-GM Datasheet - Page 201

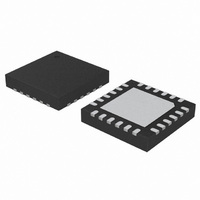

C8051F988-GM

Manufacturer Part Number

C8051F988-GM

Description

IC MCU 8BIT 4KB FLASH 24QFN

Manufacturer

Silicon Laboratories Inc

Series

C8051F9xxr

Specifications of C8051F988-GM

Program Memory Type

FLASH

Program Memory Size

4KB (4K x 8)

Package / Case

24-UQFN Exposed Pad, 24-HUQFN

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT

Number Of I /o

17

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 3.6 V

Data Converters

A/D 10x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Processor Series

C8051F9x

Core

8051

Data Ram Size

512 B

Interface Type

I2C, SMBus, Enhanced UART, Enhanced SPI

Maximum Clock Frequency

7 KHz

Number Of Programmable I/os

17

Number Of Timers

4

Operating Supply Voltage

2.4 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Development Tools By Supplier

C8051F996DK

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 10 Channel

On-chip Dac

10 bit, 4 Channel

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

336-1959-5

- Current page: 201 of 322

- Download datasheet (3Mb)

20.2. SmaRTClock Clocking Sources

The SmaRTClock peripheral is clocked from its own timebase, independent of the system clock. The

SmaRTClock timebase can be derived from an external CMOS clock, the internal LFO, or the SmaRT-

Clock oscillator circuit, which has two modes of operation: Crystal Mode, and Self-Oscillate Mode. The

oscillation frequency is 32.768 kHz in Crystal Mode and can be programmed in the range of 10 kHz to

40 kHz in Self-Oscillate Mode. The internal LFO frequency is 16.4 kHz ±20%. The frequency of the

SmaRTClock oscillator can be measured with respect to another oscillator using an on-chip timer. See

Section “25. Timers” on page 276 for more information on how this can be accomplished.

Note: The SmaRTClock timebase can be selected as the system clock and routed to a port pin. See Section

20.2.1. Using the SmaRTClock Oscillator with a Crystal or External CMOS Clock

When using Crystal Mode, a 32.768 kHz crystal should be connected between XTAL3 and XTAL4. No

other external components are required. The following steps show how to start the SmaRTClock crystal

oscillator in software:

1. Configure the XTAL3 and XTAL4 pins for Analog I/O.

2. Set SmaRTClock to Crystal Mode (XMODE = 1).

3. Disable Automatic Gain Control (AGCEN) and enable Bias Doubling (BIASX2) for fast crystal startup.

4. Set the desired loading capacitance (RTC0XCF).

5. Enable power to the SmaRTClock oscillator circuit (RTC0EN = 1).

6. Wait 20 ms.

7. Poll the SmaRTClock Clock Valid Bit (CLKVLD) until the crystal oscillator stabilizes.

8. Poll the SmaRTClock Load Capacitance Ready Bit (LOADRDY) until the load capacitance reaches its

9. Enable Automatic Gain Control (AGCEN) and disable Bias Doubling (BIASX2) for maximum power

10.Enable the SmaRTClock missing clock detector.

11. Wait 2 ms.

12.Clear the PMU0CF wake-up source flags.

In Crystal Mode, the SmaRTClock oscillator may be driven by an external CMOS clock. The CMOS clock

should be applied to XTAL3. XTAL34 should be left floating. In this mode, the external CMOS clock is ac

coupled into the SmaRTClock and should have a minimum voltage swing of 400 mV. The CMOS clock sig-

nal voltage should not exceed VDD or drop below GND. Bias levels closer to VDD will result in lower I/O

power consumption because the XTAL3 pin has a built-in weak pull-up. The SmaRTClock oscillator should

be configured to its lowest bias setting with AGC disabled. The CLKVLD bit is indeterminate when using a

CMOS clock, however, the OSCFAIL bit may be checked 2 ms after SmaRTClock oscillator is powered on

to ensure that there is a valid clock on XTAL3.

programmed value.

savings.

“19. Clocking Sources” on page 186 for information on selecting the system clock source and Section “21. Port

Input/Output” on page 213 for information on how to route the system clock to a port pin. The SmaRTClock

timebase can also be routed to a port pin while the device is in its ultra low power sleep mode. See the

PMU0MD register description for details.

Rev. 1.0

C8051F99x-C8051F98x

201

Related parts for C8051F988-GM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

SMD/C°/SINGLE-ENDED OUTPUT SILICON OSCILLATOR

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 AES KEYFOB DEMO WITH LCD RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A N/A/SI4010 SIMPLIFIED KEY FOB DEMO WITH LED RX

Manufacturer:

Silicon Laboratories Inc

Datasheet:

Part Number:

Description:

N/A/-40 TO 85 OC/EZLINK MODULE; F930/4432 HIGH BAND (REV E/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

EZLink Module; F930/4432 Low Band (rev e/B1)

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4460 10 DBM RADIO TEST CARD 434 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4461 14 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RFSWITCH RADIO TEST CARD 460 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 27 DBM RADIO TEST CARD 868 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 SKYWORKS 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

N/A N/A/-40 TO 85 OC/4463 RFMD 30 DBM RADIO TEST CARD 915 MHZ

Manufacturer:

Silicon Laboratories Inc

Part Number:

Description:

I°/4463 20 DBM RADIO TEST CARD 169 MHZ

Manufacturer:

Silicon Laboratories Inc