MPC8313E-RDB Freescale Semiconductor, MPC8313E-RDB Datasheet - Page 79

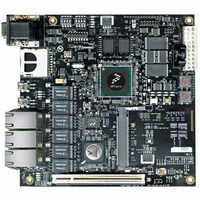

MPC8313E-RDB

Manufacturer Part Number

MPC8313E-RDB

Description

BOARD PROCESSOR

Manufacturer

Freescale Semiconductor

Series

PowerQUICC II™ PROr

Type

MCUr

Datasheets

1.MPC8313CZQAFFB.pdf

(100 pages)

2.MPC8313E-RDBB.pdf

(52 pages)

3.MPC8313E-RDBB.pdf

(2 pages)

Specifications of MPC8313E-RDB

Contents

Reference Design Board, Software and Documentation

Termination Type

SMD

Supply Voltage Max

1.05V

Tool / Board Applications

Wired Connectivity-LIN, CAN, Ethernet, USB

Mcu Supported Families

POWERQUICC II PRO

Rohs Compliant

Yes

Filter Terminals

SMD

Silicon Manufacturer

Freescale

Silicon Core Number

MPC83xx

Kit Application Type

Communication & Networking

Application Sub Type

Ethernet

Core Architecture

Power Architecture

Silicon Family Name

PowerQUICC II PRO

For Use With/related Products

MPC8313E

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Table 65

conditions (see

20.1

The system PLL is controlled by the RCWL[SPMF] parameter.

encodings for the system PLL.

Freescale Semiconductor

provides the operating frequencies for the MPC8313E TEPBGAII under recommended operating

System PLL Configuration

TSEC1

TSEC2

Security Core, I

USB DR

PCI and DMA complex

e300 core frequency ( core_clk )

Coherent system bus frequency ( csb_clk )

DDR1/2 memory bus frequency (MCK)

Local bus frequency (LCLK n )

PCI input frequency (SYS_CLK_IN or PCI_CLK)

Notes:

1. The SYS_CLK_IN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be

2. The DDR data rate is 2x the DDR memory bus frequency.

3. The local bus frequency is 1/2, 1/4, or 1/8 of the lbc_clk frequency (depending on

Table

chosen such that the resulting csb_clk , MCK, LCLK[0:1], and core_clk frequencies do not

exceed their respective maximum or minimum operating frequencies. The value of

SCCR[ENCCM] and SCCR[USBDRCM] must be programmed such that the maximum

internal operating frequency of the security core and USB modules do not exceed their

respective value listed in this table.

LCCR[CLKDIV]), which is in turn, 1x or 2x the csb_clk frequency (depending on

RCWL[LBCM]).

MPC8313E PowerQUICC

2).

Unit

2

C, SAP, TPR

Characteristic

Table 65. Operating Frequencies for TEPBGAII

Table 66. System PLL Multiplication Factors

RCWL[SPMF]

Table 64. Configurable Clock Units

0000

0001

0010

3

™

1

II Pro Processor Hardware Specifications, Rev. 3

Frequency

Default

csb_clk

csb_clk

csb_clk

csb_clk

csb_clk

2

Multiplication Factor

Off, csb_clk, csb_clk /2, csb_clk /3

Off, csb_clk, csb_clk /2, csb_clk /3

Off, csb_clk, csb_clk /2, csb_clk /3

Off, csb_clk, csb_clk /2,

Off, csb_clk

System PLL

Operating Frequency

Reserved

Reserved

× 2

Maximum

Table 66

333

167

167

66

66

Options

shows the multiplication factor

csb_clk

Unit

MHz

MHz

MHz

MHz

MHz

/3

Clocking

79