MPC8313E-RDB Freescale Semiconductor, MPC8313E-RDB Datasheet - Page 2

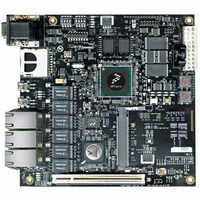

MPC8313E-RDB

Manufacturer Part Number

MPC8313E-RDB

Description

BOARD PROCESSOR

Manufacturer

Freescale Semiconductor

Series

PowerQUICC II™ PROr

Type

MCUr

Datasheets

1.MPC8313CZQAFFB.pdf

(100 pages)

2.MPC8313E-RDBB.pdf

(52 pages)

3.MPC8313E-RDBB.pdf

(2 pages)

Specifications of MPC8313E-RDB

Contents

Reference Design Board, Software and Documentation

Termination Type

SMD

Supply Voltage Max

1.05V

Tool / Board Applications

Wired Connectivity-LIN, CAN, Ethernet, USB

Mcu Supported Families

POWERQUICC II PRO

Rohs Compliant

Yes

Filter Terminals

SMD

Silicon Manufacturer

Freescale

Silicon Core Number

MPC83xx

Kit Application Type

Communication & Networking

Application Sub Type

Ethernet

Core Architecture

Power Architecture

Silicon Family Name

PowerQUICC II PRO

For Use With/related Products

MPC8313E

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Overview

1

The MPC8313E incorporates the e300c3 core, which includes 16 Kbytes of L1 instruction and data caches

and on-chip memory management units (MMUs). The MPC8313E has interfaces to dual enhanced

three-speed 10/100/1000 Mbps Ethernet controllers, a DDR1/DDR2 SDRAM memory controller, an

enhanced local bus controller, a 32-bit PCI controller, a dedicated security engine, a USB 2.0 dual-role

controller and an on-chip full-speed PHY, a programmable interrupt controller, dual I

4-channel DMA controller, and a general-purpose I/O port. A block diagram of the MPC8313E is shown

in

The MPC8313E security engine (SEC 2.2) allows CPU-intensive cryptographic operations to be offloaded

from the main CPU core. The security-processing accelerator provides hardware acceleration for the DES,

3DES, AES, SHA-1, and MD-5 algorithms.

1.1

The following features are supported in the MPC8313E:

2

Figure

•

•

•

•

•

•

•

•

PCI

Overview

Embedded PowerPC™ e300 processor core built on Power Architecture™ technology; operates at

up to 333 MHz.

High-performance, low-power, and cost-effective host processor

DDR1/DDR2 memory controller—one 16-/32-bit interface at up to 333 MHz supporting both

DDR1 and DDR2

16-Kbyte instruction cache and 16-Kbyte data cache, a floating point unit, and two integer units

Peripheral interfaces such as 32-bit PCI interface with up to 66-MHz operation, 16-bit enhanced

local bus interface with up to 66-MHz operation, and USB 2.0 (full speed) with an on-chip PHY.

Security engine provides acceleration for control and data plane security protocols

Power management controller for low-power consumption

High degree of software compatibility with previous-generation PowerQUICC processor-based

designs for backward compatibility and easier software migration

1.

MPC8313E Features

Dual I

DUART

Timers

GPIO

DMA

2

C

I/O Sequencer

(IOS)

MPC8313E PowerQUICC

Note: The MPC8313 does not include a security engine.

Controller

Interrupt

Security Engine 2.2

Figure 1. MPC8313E Block Diagram

™

II Pro Processor Hardware Specifications, Rev. 3

I-Cache

e300c3 Core w/FPU and

16-KB

Power Management

Host/Device/OTG

ULPI

USB 2.0

D-Cache

16-KB

On-Chip

FS PHY

Gb Ethernet

MAC

Local Bus,

SPI

Freescale Semiconductor

2

C controllers, a

Gb Ethernet

DDR1/DDR2

MAC

Controller