CYII5SC1300-EVAL Cypress Semiconductor Corp, CYII5SC1300-EVAL Datasheet - Page 2

CYII5SC1300-EVAL

Manufacturer Part Number

CYII5SC1300-EVAL

Description

BOARD EVAL IMG SENS IBIS5-B-1300

Manufacturer

Cypress Semiconductor Corp

Specifications of CYII5SC1300-EVAL

Sensor Type

CMOS Imaging, Color (RGB)

Sensing Range

1.3 Megapixel

Interface

Parallel/Serial

Sensitivity

106 fps

Voltage - Supply

3 V ~ 4.5 V

Embedded

No

Utilized Ic / Part

IBIS5-B-1300

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant, Contains lead / RoHS non-compliant

Document #: 38-05710 Rev. *A

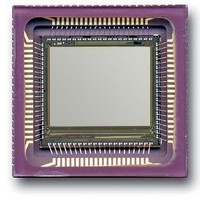

Architecture and Operation

In this part the most important blocks of the sensor are described in more detail.

Floor Plan

Figure 1

sensor. It consists basically of a pixel array, one X- and two

Y-addressing registers for the readout in X- and Y-direction,

column amplifiers that correct for the fixed pattern noise, an

analog multiplexer, and an analog output amplifier.

The left Y-addressing register is used for readout operation.

The right Y-addressing register is used for reset of pixel rows.

In multiple slope synchronous shutter mode, the right

Y-addressing register resets the whole pixel core with a

lowered reset voltage. In rolling curtain shutter mode, the right

Y-addressing register is used for the reset pointer in single and

double slope operation to reset 1 pixel row.

Most of the signals for the image core are generated by the

on-chip sequencer. Some basic signals (like start/stop

integration, line and frame sync signals, etc.) have to be

generated externally.

A 10-bit ADC is implemented on chip but electrically isolated

from the image core. The analog pixel output has to be routed

to the analog ADC input on the outside.

shows the architecture of the IBIS5-B-1300 image

addressing

Y-left

Pixel

Figure 1. Block Diagram of the IBIS5-B-1300 Image Sensor

Column amplifiers

X-addressing

Analog multiplexer

Pixel core

Imager core

Y-right

addressing

Output

amplifier

Pixel

The pixel architecture and the color filter array are described

below.

Architecture

The pixel architecture used in the IBIS5-B-1300 is a

4-transistor pixel as shown in

implemented using the high fill factor technique as patented by

Cypress (US patent No. 6,225,670 and others). The 4T-pixel

features a snapshot shutter but can also emulate the 3T-pixel

by continuously closing sampling switch M2. Using M4 as a

global sample transistor for all pixels enables the snapshot

shutter mode. Due to this pixel architecture, integration during

read out is not possible in synchronous shutter mode.

ADC

Sequencer

Sensor

M1

Figure 2. Architecture of the 4T-pixel

reset

sample

System clock

40 MHz

M2

External

connection

C

M3

Sample

Reset

Figure

CYII5FM1300AB

mux

M4

C

Column output

IBIS5-B-1300

2. The pixel has been

Select

column

output

Page 2 of 42

[+] Feedback