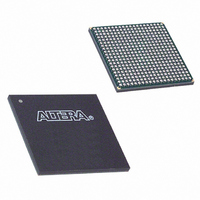

EP1C20F400C6N Altera, EP1C20F400C6N Datasheet - Page 19

EP1C20F400C6N

Manufacturer Part Number

EP1C20F400C6N

Description

IC CYCLONE FPGA 20K LE 400-FBGA

Manufacturer

Altera

Series

Cyclone®r

Datasheet

1.EP1C3T144C8.pdf

(106 pages)

Specifications of EP1C20F400C6N

Number Of Logic Elements/cells

20060

Number Of Labs/clbs

2006

Total Ram Bits

294912

Number Of I /o

301

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

400-FBGA

Family Name

Cyclone®

Number Of Logic Blocks/elements

20060

# I/os (max)

301

Frequency (max)

405.2MHz

Process Technology

0.13um (CMOS)

Operating Supply Voltage (typ)

1.5V

Logic Cells

20060

Ram Bits

294912

Operating Supply Voltage (min)

1.425V

Operating Supply Voltage (max)

1.575V

Operating Temp Range

0C to 85C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

400

Package Type

FBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Lead Free Status / Rohs Status

Compliant

Other names

544-1687

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1C20F400C6N

Manufacturer:

ALTERA

Quantity:

237

Altera Corporation

May 2008

migrating through different device densities. Dedicated row

interconnects route signals to and from LABs, PLLs, and M4K memory

blocks within the same row. These row resources include:

■

■

The direct link interconnect allows a LAB or M4K memory block to drive

into the local interconnect of its left and right neighbors. Only one side of

a PLL block interfaces with direct link and row interconnects. The direct

link interconnect provides fast communication between adjacent LABs

and/or blocks without using row interconnect resources.

The R4 interconnects span four LABs, or two LABs and one M4K RAM

block. These resources are used for fast row connections in a four-LAB

region. Every LAB has its own set of R4 interconnects to drive either left

or right.

interconnects can drive and be driven by M4K memory blocks, PLLs, and

row IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive

a given R4 interconnect. For R4 interconnects that drive to the right, the

primary LAB and right neighbor can drive on to the interconnect. For R4

interconnects that drive to the left, the primary LAB and its left neighbor

can drive on to the interconnect. R4 interconnects can drive other R4

interconnects to extend the range of LABs they can drive. R4

interconnects can also drive C4 interconnects for connections from one

row to another.

Direct link interconnects between LABs and adjacent blocks

R4 interconnects traversing four blocks to the right or left

Figure 2–9

shows R4 interconnect connections from a LAB. R4

MultiTrack Interconnect

Preliminary

2–13