AT89C51CC03CA-RLTUM Atmel, AT89C51CC03CA-RLTUM Datasheet - Page 115

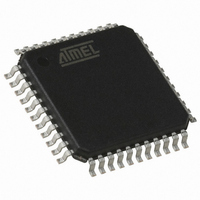

AT89C51CC03CA-RLTUM

Manufacturer Part Number

AT89C51CC03CA-RLTUM

Description

IC 8051 MCU 64K FLASH 44-VQFP

Manufacturer

Atmel

Series

AT89C CANr

Datasheet

1.AT89C51CC03C-S3RIM.pdf

(198 pages)

Specifications of AT89C51CC03CA-RLTUM

Core Processor

8051

Core Size

8-Bit

Speed

40MHz

Connectivity

CAN, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

36

Program Memory Size

64KB (64K x 8)

Program Memory Type

FLASH

Eeprom Size

2K x 8

Ram Size

2.25K x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

44-TQFP, 44-VQFP

Processor Series

AT89x

Core

8051

Data Bus Width

8 bit

Data Ram Size

2304 B

Interface Type

UART, SPI

Maximum Clock Frequency

60 MHz

Number Of Programmable I/os

36

Number Of Timers

2

Operating Supply Voltage

3 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

PK51, CA51, A51, ULINK2

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

Package

44VQFP

Device Core

8051

Family Name

AT89

Maximum Speed

60 MHz

For Use With

AT89OCD-01 - USB EMULATOR FOR AT8XC51 MCU

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT89C51CC03CA-RLTUM

Manufacturer:

ADI

Quantity:

141

- Current page: 115 of 198

- Download datasheet (3Mb)

4182O–CAN–09/08

Table 61. CANBT2 Register

CANBT2 (S:B5h)

CAN Bit Timing Registers 2

Note:

No default value after reset.

Number

Bit

6-5

3-1

7

-

7

4

0

The CAN controller bit timing registers must be accessed only if the CAN controller is dis-

abled with the ENA bit of the CANGCON register set to 0.

See Figure 52.

Bit Mnemonic Description

SJW 1

SJW1:0

PRS2:0

6

-

-

-

SJW 0

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Re-synchronization Jump Width

To compensate for phase shifts between clock oscillators of different bus

controllers, the controller must re-synchronize on any relevant signal edge of

the current transmission.

The synchronization jump width defines the maximum number of clock cycles.

A bit period may be shortened or lengthened by a re-synchronization.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

Programming Time Segment

This part of the bit time is used to compensate for the physical delay times

within the network. It is twice the sum of the signal propagation time on the

bus line, the input comparator delay and the output driver delay.

Reserved

The value read from this bit is indeterminate. Do not set this bit.

5

4

-

Tsjw = Tscl x (SJW [1..0] +1)

Tprs = Tscl x (PRS[2..0] + 1)

PRS 2

3

PRS 1

AT89C51CC03

2

PRS 0

1

0

-

115

Related parts for AT89C51CC03CA-RLTUM

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

At89c51cc03 Enhanced 8-bit Mcu With Can Controller And Flash Memory

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: