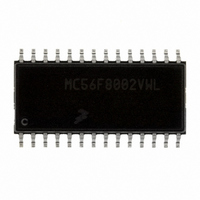

MC56F8002VWL Freescale Semiconductor, MC56F8002VWL Datasheet - Page 5

MC56F8002VWL

Manufacturer Part Number

MC56F8002VWL

Description

DSC 12K FLASH 32MHZ 28-SOIC

Manufacturer

Freescale Semiconductor

Series

56F8xxxr

Datasheet

1.MC56F8006DEMO.pdf

(100 pages)

Specifications of MC56F8002VWL

Core Processor

56800

Core Size

16-Bit

Speed

32MHz

Connectivity

I²C, LIN, SCI, SPI

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

23

Program Memory Size

12KB (6K x 16)

Program Memory Type

FLASH

Ram Size

1K x 16

Voltage - Supply (vcc/vdd)

1.8 V ~ 3.6 V

Data Converters

A/D 15x12b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 105°C

Package / Case

28-SOIC

Product

DSCs

Data Bus Width

16 bit

Processor Series

MC56F80xx

Core

56800E

Instruction Set Architecture

Dual Harvard

Device Million Instructions Per Second

32 MIPs

Maximum Clock Frequency

32 MHz

Number Of Programmable I/os

40

Data Ram Size

2 KB

Operating Supply Voltage

1.8 V to 3.6 V

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

Development Tools By Supplier

MC56F8006DEMO, APMOTOR56F8000E

Interface Type

LIN, I2C, SCI, SPI

Minimum Operating Temperature

- 40 C

For Use With

APMOTOR56F8000E - KIT DEMO MOTOR CTRL SYSTEM

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

MC56F8002VWL

Manufacturer:

FREESCALE

Quantity:

20 000

3.1.2

3.1.3

3.1.4

3.1.5

Freescale Semiconductor

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Parallel instruction set with unique DSP addressing modes

Hardware DO and REP loops

Three internal address buses

Four internal data buses

Instruction set supports DSP and controller functions

Controller-style addressing modes and instructions for compact code

Efficient C compiler and local variable support

Software subroutine and interrupt stack with depth limited only by memory

JTAG/enhanced on-chip emulation (EOnCE) for unobtrusive, processor speed–independent, real-time debugging

1.8 V to 3.6 V operation (power supplies and I/O)

From power-on-reset: approximately 1.9 V to 3.6 V

Ambient temperature operating range: –40 °C to 105 °C

Dual Harvard architecture permits as many as three simultaneous accesses to program and data memory

Flash security and protection that prevent unauthorized users from gaining access to the internal flash

On-chip memory

— 16 KB of program flash for 56F8006 and 12 KB of program flash for 56F8002

— 2 KB of unified data/program RAM

EEPROM emulation capability using flash

Five interrupt priority levels

— Three user programmable priority levels for each interrupt source: Level 0, 1, 2

— Unmaskable level 3 interrupts include: illegal instruction, hardware stack overflow, misaligned data access, SWI3

— Lowest-priority software interrupt: level LP

Allow nested interrupt that higher priority level interrupt request can interrupt lower priority interrupt subroutine

The masking of interrupt priority level is managed by the 56800E core

One programmable fast interrupt that can be assigned to any interrupt source

Notification to system integration module (SIM) to restart clock out of wait and stop states

Ability to relocate interrupt vector table

One multi-function, six-output pulse width modulator (PWM) module

— Up to 96 MHz PWM operating clock

— 15 bits of resolution

— Center-aligned and edge-aligned PWM signal mode

— Phase shifting PWM pulse generation

— Four programmable fault inputs with programmable digital filter

instruction. Maskable level 3 interrupts include: EOnCE step counter, EOnCE breakpoint unit, EOnCE trace

buffer

Operation Range

Memory

Interrupt Controller

Peripheral Highlights

MC56F8006/MC56F8002 Digital Signal Controller, Rev. 3

Overview

5