MC908AP32CFAE Freescale Semiconductor, MC908AP32CFAE Datasheet - Page 217

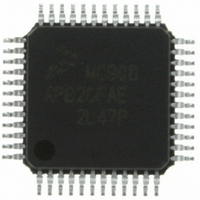

MC908AP32CFAE

Manufacturer Part Number

MC908AP32CFAE

Description

IC MCU 32K FLASH 8MHZ 48-LQFP

Manufacturer

Freescale Semiconductor

Series

HC08r

Specifications of MC908AP32CFAE

Core Processor

HC08

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, IRSCI, SCI, SPI

Peripherals

LED, LVD, POR, PWM

Number Of I /o

32

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

48-LQFP

Controller Family/series

HC08

No. Of I/o's

32

Ram Memory Size

2KB

Cpu Speed

8MHz

No. Of Timers

2

Embedded Interface Type

I2C, SCI, SPI

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC908AP32CFAE

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC908AP32CFAER

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

- Current page: 217 of 316

- Download datasheet (2Mb)

When configured as a slave (SPMSTR = 0), the MODF flag is set if SS goes high during a transmission.

When CPHA = 0, a transmission begins when SS goes low and ends once the incoming SPSCK goes

back to its idle level following the shift of the eighth data bit. When CPHA = 1, the transmission begins

when the SPSCK leaves its idle level and SS is already low. The transmission continues until the SPSCK

returns to its idle level following the shift of the last data bit. (See

In a slave SPI (MSTR = 0), the MODF bit generates an SPI receiver/error CPU interrupt request if the

ERRIE bit is set. The MODF bit does not clear the SPE bit or reset the SPI in any way. Software can abort

the SPI transmission by clearing the SPE bit of the slave.

To clear the MODF flag, read the SPSCR with the MODF bit set and then write to the SPCR register. This

entire clearing mechanism must occur with no MODF condition existing or else the flag is not cleared.

13.8 Interrupts

Four SPI status flags can be enabled to generate CPU interrupt requests.

Freescale Semiconductor

SPTE

Transmitter empty

SPRF

Receiver full

OVRF

Overflow

MODF

Mode fault

To prevent bus contention with another master SPI after a mode fault error,

clear all SPI bits of the data direction register of the shared I/O port before

enabling the SPI.

Setting the MODF flag does not clear the SPMSTR bit. The SPMSTR bit

has no function when SPE = 0. Reading SPMSTR when MODF = 1 shows

the difference between a MODF occurring when the SPI is a master and

when it is a slave.

When CPHA = 0, a MODF occurs if a slave is selected (SS is at logic 0) and

later unselected (SS is at logic 1) even if no SPSCK is sent to that slave.

This happens because SS at logic 0 indicates the start of the transmission

(MISO driven out with the value of MSB) for CPHA = 0. When CPHA = 1, a

slave can be selected and then later unselected with no transmission

occurring. Therefore, MODF does not occur since a transmission was

never begun.

A logic 1 voltage on the SS pin of a slave SPI puts the MISO pin in a high

impedance state. Also, the slave SPI ignores all incoming SPSCK clocks,

even if it was already in the middle of a transmission.

Flag

MC68HC908AP A-Family Data Sheet, Rev. 3

SPI transmitter CPU interrupt request

(SPTIE = 1, SPE = 1)

SPI receiver CPU interrupt request

SPI receiver/error interrupt request (ERRIE = 1)

SPI receiver/error interrupt request (ERRIE = 1)

(SPRIE = 1)

Table 13-2. SPI Interrupts

NOTE

NOTE

NOTE

Request

13.5 Transmission

Formats.)

Interrupts

217

Related parts for MC908AP32CFAE

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet:

Part Number:

Description:

Manufacturer:

Freescale Semiconductor, Inc

Datasheet: