PI7C9X20404GPBNBE Pericom Semiconductor, PI7C9X20404GPBNBE Datasheet - Page 5

PI7C9X20404GPBNBE

Manufacturer Part Number

PI7C9X20404GPBNBE

Description

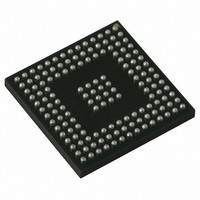

IC PCIE PACKET SWITCH 148LFBGA

Manufacturer

Pericom Semiconductor

Series

GreenPacket™r

Datasheet

1.PI7C9X20404GPBNBE.pdf

(79 pages)

Specifications of PI7C9X20404GPBNBE

Applications

Data Transport

Interface

Advanced Configuration Power Interface (ACPI)

Package / Case

148-LFBGA

Mounting Type

Surface Mount

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Voltage - Supply

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

PI7C9X20404GPBNBE

Manufacturer:

RICHTEK

Quantity:

770

TABLE OF CONTENTS

1

2

3

4

5

6

7

June 2009 – Revision 1.6

Pericom Semiconductor

3.1

3.2

3.3

3.4

3.5

3.6

4.1

5.1

5.2

5.3

5.4

5.5

5.6

5.7

5.8

5.9

5.10

5.11

6.1

6.2

7.1

7.2

FEATURES.........................................................................................................................................................10

GENERAL DESCRIPTION..............................................................................................................................11

PIN DESCRIPTION...........................................................................................................................................12

PIN ASSIGNMENTS .........................................................................................................................................15

FUNCTIONAL DESCRIPTION.......................................................................................................................16

EEPROM INTERFACE AND SYSTEM MANAGEMENT BUS..................................................................22

REGISTER DESCRIPTION.............................................................................................................................30

5.6.1

5.6.2

5.6.3

5.6.4

5.6.5

6.1.1

6.1.2

6.1.3

6.1.4

7.2.1

7.2.2

7.2.3

7.2.4

7.2.5

PCI EXPRESS INTERFACE SIGNALS ....................................................................................................12

PORT CONFIGURATION SIGNALS .......................................................................................................12

HOT PLUG SIGNALS ...............................................................................................................................13

MISCELLANEOUS SIGNALS..................................................................................................................13

JTAG BOUNDARY SCAN SIGNALS ......................................................................................................14

POWER PINS.............................................................................................................................................14

PIN LIST

PHYSICAL LAYER CIRCUIT ..................................................................................................................16

DATA LINK LAYER (DLL)......................................................................................................................18

TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION) ..............................................18

ROUTING ..................................................................................................................................................18

TC/VC MAPPING......................................................................................................................................19

QUEUE.......................................................................................................................................................19

TRANSACTION ORDERING...................................................................................................................20

PORT ARBITRATION ..............................................................................................................................21

VC ARBITRATION ...................................................................................................................................21

FLOW CONTROL .....................................................................................................................................21

TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION) .............................................21

EEPROM INTERFACE .............................................................................................................................22

SMB

REGISTER TYPES ....................................................................................................................................30

TRANSPARENT MODE CONFIGURATION REGISTERS ....................................................................30

PH .......................................................................................................................................................19

PD .......................................................................................................................................................19

NPHD .................................................................................................................................................19

CPLH ..................................................................................................................................................19

CPLD ..................................................................................................................................................20

AUTO MODE EERPOM ACCESS .....................................................................................................22

EEPROM MODE AT RESET..............................................................................................................22

EEPROM SPACE ADDRESS MAP ....................................................................................................22

MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS..........................................24

VENDOR ID REGISTER – OFFSET 00h ...........................................................................................32

DEVICE ID REGISTER – OFFSET 00h.............................................................................................32

COMMAND REGISTER – OFFSET 04h............................................................................................32

PRIMARY STATUS REGISTER – OFFSET 04h.................................................................................33

REVISION ID REGISTER – OFFSET 08h .........................................................................................33

US

INTERFACE .................................................................................................................................29

OF

148-PIN LFBGA....................................................................................................................15

Page 5 of 79

4Port-4Lane PCI Express Switch

GreenPacket

PI7C9X20404GP

Datasheet

TM

Family