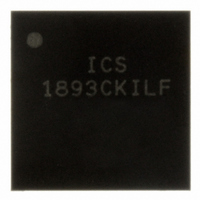

ICS1893CKILF IDT, Integrated Device Technology Inc, ICS1893CKILF Datasheet - Page 47

ICS1893CKILF

Manufacturer Part Number

ICS1893CKILF

Description

PHYCEIVER LOW PWR 3.3V 56-MLF2

Manufacturer

IDT, Integrated Device Technology Inc

Series

PHYceiver™r

Type

PHY Transceiverr

Datasheet

1.ICS1893CFLFT.pdf

(127 pages)

Specifications of ICS1893CKILF

Protocol

MII

Voltage - Supply

3.14 V ~ 3.47 V

Mounting Type

Surface Mount

Package / Case

56-VQFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Drivers/receivers

-

Lead Free Status / RoHS Status

Compliant, Lead free / RoHS Compliant

Other names

1893CKILF

800-1023

800-1023

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ICS1893CKILF

Manufacturer:

IDT

Quantity:

206

Company:

Part Number:

ICS1893CKILFT

Manufacturer:

ST

Quantity:

785

Part Number:

ICS1893CKILFT

Manufacturer:

ICS

Quantity:

20 000

7.2.2 Loopback Enable (bit 0.14)

7.2.3 Data Rate Select (bit 0.13)

7.2.4 Auto-Negotiation Enable (bit 0.12)

ICS1893CF, Rev. K, 05/13/10

This bit controls the Loopback mode for the ICS1893CF. Setting this bit to logic:

•

•

This bit provides a means of controlling the ICS1893CF data rate. Its operation depends on the state of

several other functions, including the HW/SW input pin and the Auto-Negotiation Enable bit (bit 0.12).

When the ICS1893CF is configured for:

•

•

This bit provides a means of controlling the ICS1893CF Auto-Negotiation sublayer. Its operation depends

on the HW/SW input pin.

When the ICS1893CF is configured for:

•

•

Zero disables the Loopback mode.

One enables the Loopback mode by disabling the Twisted-Pair Transmitter, the Twisted-Pair Receiver,

and the collision detection circuitry. (The STA can override the ICS1893CF from disabling the collision

detection circuitry in Loopback mode by writing logic one to bit 0.7.) When the ICS1893CF is in

Loopback mode, the data presented at the MAC transmit interface is internally looped back to the MAC

receive interface. The delay from the assertion of Transmit Data Enable (TXEN) to the assertion of

Receive Data valid (RXDV) is less than 512 bit times.

Hardware mode (that is, the HW/SW pin is logic zero), the ICS1893CF isolates this bit 0.13 and uses the

10/100SEL input pin to establish the data rate for the ICS1893CF. In this Hardware mode:

Software mode (that is, the HW/SW pin is logic one), the function of bit 0.13 depends on the

Auto-Negotiation Enable bit 0.12. When the Auto-Negotiation sublayer is:

Hardware mode, (that is, the HW/SW pin is logic zero), the ICS1893CF isolates bit 0.12 and uses the

ANSEL (Auto-Negotiation Select) input pin to determine whether to enable the Auto-Negotiation

sublayer.

Note: In Hardware mode, bit 0.12 is undefined.

Software mode, (that is, the HW/SW pin is logic one), bit 0.12 determines whether to enable the

Auto-Negotiation sublayer. When bit 0.12 is logic:

– Bit 0.13 is undefined.

– The ICS1893CF provides a Data Rate Status bit (in the QuickPoll Detailed Status Register, bit

– Enabled, the ICS1893CF isolates bit 0.13 and relies on the results of the auto-negotiation process to

– Disabled, bit 0.13 determines the data rate. In this case, setting bit 0.13 to logic:

– Zero:

– One:

17.15), which always shows the setting of an active link.

establish the data rate.

• Zero selects 10-Mbps ICS1893CF operations.

• One selects 100-Mbps ICS1893CF operations.

• The ICS1893CF disables the Auto-Negotiation sublayer.

• The ICS1893CF bit 0.13 (the Data Rate bit) and bit 0.8 (the Duplex Mode bit) determine the data

• The ICS1893CF enables the Auto-Negotiation sublayer.

• The ICS1893CF isolates bit 0.13 and bit 0.8.

ICS1893CF Data Sheet Rev. J - Release

rate and the duplex mode.

Copyright © 2009, Integrated Device Technology, Inc.

All rights reserved.

47

Chapter 7 Management Register Set

May, 2010