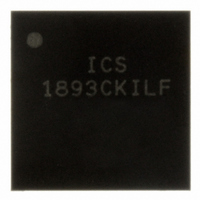

ICS1893CKILF IDT, Integrated Device Technology Inc, ICS1893CKILF Datasheet - Page 11

ICS1893CKILF

Manufacturer Part Number

ICS1893CKILF

Description

PHYCEIVER LOW PWR 3.3V 56-MLF2

Manufacturer

IDT, Integrated Device Technology Inc

Series

PHYceiver™r

Type

PHY Transceiverr

Datasheet

1.ICS1893CFLFT.pdf

(127 pages)

Specifications of ICS1893CKILF

Protocol

MII

Voltage - Supply

3.14 V ~ 3.47 V

Mounting Type

Surface Mount

Package / Case

56-VQFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Drivers/receivers

-

Lead Free Status / RoHS Status

Compliant, Lead free / RoHS Compliant

Other names

1893CKILF

800-1023

800-1023

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ICS1893CKILF

Manufacturer:

IDT

Quantity:

206

Company:

Part Number:

ICS1893CKILFT

Manufacturer:

ST

Quantity:

785

Part Number:

ICS1893CKILFT

Manufacturer:

ICS

Quantity:

20 000

4.1.2 Specific Reset Operations

4.1.2.1 Hardware Reset

4.1.2.2 Power-On Reset

ICS1893CF, Rev. K, 05/13/10

This section discusses the following specific ways that the ICS1893CF can be reset:

•

•

•

Note:

Entering Hardware Reset

Holding the active-low RESETn pin low for a minimum of five REF_IN clock cycles initiates a hardware

reset (that is, the ICS1893CF enters the reset state). During reset, the ICS1893CF executes the steps

listed in

Exiting Hardware Reset

After the signal on the RESETn pin transitions from a low to a high state, the ICS1893CF completes in 640

ns (that is, in 16 REF_IN clocks) steps 1 through 5, listed in

five steps are completed, the Serial Management Port is ready for normal operations, but this action does

not signify the end of the reset cycle. The reset cycle completes when the transmit clock (TXCLK) and

receive clock (RXCLK) are available, which is typically 53 ms after the RESETn pin goes high. [For details

on this transition, see

Note:

1. The MAC Interface is not available for use until the TXCLK and RXCLK are valid.

2. The Control Register bit 0.15 does not represent the status of a hardware reset. It is a self-clearing bit

Entering Power-On Reset

When power is applied to the ICS1893CF, it waits until the potential between VDD and VSS achieves a

minimum voltage before entering reset and executing the steps listed in

After entering reset from a power-on condition, the ICS1893CF remains in reset for approximately 20 µs.

(For details on this transition, see

Exiting Power-On Reset

The ICS1893CF automatically exits reset and performs the same steps as for a hardware reset. (See

Section 4.1.1.2, “Exiting

Note:

Hardware reset (using the RESETn pin)

Power-on reset (applying power to the ICS1893CF)

Software reset (using Control Register bit 0.15)

that is used to initiate a software reset.

ICS1893CF Data Sheet Rev. J - Release

At the completion of a reset (either hardware, power-on, or software), the ICS1893CF sets all

registers to their default values.

The only difference between a hardware reset and a power-on reset is that during a power-on

reset, the ICS1893CF isolates its RESETn input pin. All other functionality is the same. As with a

hardware reset, Control Register bit 0.15 does not represent the status of a power-on reset.

Section 4.1.1.1, “Entering

Section 9.5.16, “Reset: Hardware Reset and

Reset”.)

Copyright © 2009, Integrated Device Technology, Inc.

Section 9.5.15, “Reset: Power-On

Reset”.

All rights reserved.

11

Section 4.1.1.2, “Exiting

Power-Down”.]

Reset”.)

Chapter 4 Operating Modes Overview

Section 4.1.1.1, “Entering

Reset”. After the first

May, 2010

Reset”.