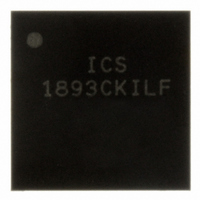

ICS1893CKILF IDT, Integrated Device Technology Inc, ICS1893CKILF Datasheet - Page 10

ICS1893CKILF

Manufacturer Part Number

ICS1893CKILF

Description

PHYCEIVER LOW PWR 3.3V 56-MLF2

Manufacturer

IDT, Integrated Device Technology Inc

Series

PHYceiver™r

Type

PHY Transceiverr

Datasheet

1.ICS1893CFLFT.pdf

(127 pages)

Specifications of ICS1893CKILF

Protocol

MII

Voltage - Supply

3.14 V ~ 3.47 V

Mounting Type

Surface Mount

Package / Case

56-VQFN

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Drivers/receivers

-

Lead Free Status / RoHS Status

Compliant, Lead free / RoHS Compliant

Other names

1893CKILF

800-1023

800-1023

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ICS1893CKILF

Manufacturer:

IDT

Quantity:

206

Company:

Part Number:

ICS1893CKILFT

Manufacturer:

ST

Quantity:

785

Part Number:

ICS1893CKILFT

Manufacturer:

ICS

Quantity:

20 000

4.1 Reset Operations

4.1.1 General Reset Operations

4.1.1.1 Entering Reset

4.1.1.2 Exiting Reset

4.1.1.3 Hot Insertion

ICS1893CF, Rev. K, 05/13/10

This section first discusses reset operations in general and then specific ways in which the ICS1893CF can

be configured for various reset options.

The following reset operations apply to all the specific ways in which the ICS1893CF can be reset, which

are discussed in

When the ICS1893CF enters a reset condition (either through hardware, power-on reset, or software), it

does the following:

1. Isolates the MAC Interface input pins

2. Drives all MAC Interface output pins low

3. Tri-states the signals on its Twisted-Pair Transmit pins (TP_TXP and TP_TXN)

4. Initializes all its internal modules and state machines to their default states

5. Enters the power-down state

6. Initializes all internal latching low (LL), latching high (LH), and latching maximum (LMX) Management

When the ICS1893CF exits a reset condition, it does the following:

1. Exits the power-down state

2. Latches the Serial Management Port Address of the ICS1893CF into the Extended Control Register,

3. Enables all its internal modules and state machines

4. Sets all Management Register bits to their default values

5. Enables the Twisted-Pair Transmit pins (TP_TXP and TP_TXN)

6. Resynchronizes both its Transmit and Receive Phase-Locked Loops, which provide its transmit clock

7. Releases all MAC Interface pins, which takes a maximum of 640 ns after the reset condition is removed

As with the ICS189X products, the ICS1893CF reset design supports ‘hot insertion’ of its MII. (That is, the

ICS1893CF can connect its MAC Interface to a MAC while power is already applied to the MAC.)

Register bits to their default values

bits 16.10:6. [See

(TXCLK) and receive clock (RXCLK)

ICS1893CF Data Sheet - Release

Section 4.1.2, “Specific Reset

Section 7.11.3, “PHY Address (bits

Copyright © 2009, Integrated Device Technology, Inc.

All rights reserved.

Operations”.

10

16.10:6)”.]

Chapter 4 Operating Modes Overview

May, 2010