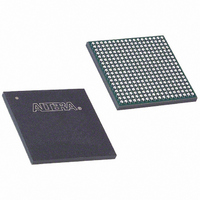

EP1C20F324C7N Altera, EP1C20F324C7N Datasheet - Page 17

EP1C20F324C7N

Manufacturer Part Number

EP1C20F324C7N

Description

IC CYCLONE FPGA 20K LE 324-FBGA

Manufacturer

Altera

Series

Cyclone®r

Datasheet

1.EP1C3T144C8.pdf

(106 pages)

Specifications of EP1C20F324C7N

Number Of Logic Elements/cells

20060

Number Of Labs/clbs

2006

Total Ram Bits

294912

Number Of I /o

233

Voltage - Supply

1.425 V ~ 1.575 V

Mounting Type

Surface Mount

Operating Temperature

0°C ~ 85°C

Package / Case

324-FBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Number Of Gates

-

Other names

544-1678

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

EP1C20F324C7N

Manufacturer:

ALTERA

Quantity:

784

Part Number:

EP1C20F324C7N

Manufacturer:

ALTERA

Quantity:

20 000

Figure 2–8. Carry Select Chain

Altera Corporation

May 2008

LAB Carry-In

A1

B1

A2

B2

A3

B3

A4

B4

A5

B5

A6

B6

A7

B7

A8

B8

A9

B9

A10

B10

LAB Carry-Out

0

0

LE1

LE2

LE3

LE4

LE5

LE6

LE7

LE8

LE9

LE10

1

1

Sum1

Sum2

Sum3

Sum4

Sum5

Sum6

Sum7

Sum8

Sum9

Sum10

Figure 2–8

One portion of the LUT generates the sum of two bits using the input

signals and the appropriate carry-in bit; the sum is routed to the output

of the LE. The register can be bypassed for simple adders or used for

accumulator functions. Another portion of the LUT generates carry-out

bits. A LAB-wide carry-in bit selects which chain is used for the addition

of given inputs. The carry-in signal for each chain, carry-in0 or

carry-in1, selects the carry-out to carry forward to the carry-in signal

of the next-higher-order bit. The final carry-out signal is routed to an LE,

where it is fed to local, row, or column interconnects.

shows the carry-select circuitry in a LAB for a 10-bit full adder.

LAB Carry-In

Carry-In0

Carry-In1

data1

data2

Carry-Out0

LUT

LUT

LUT

LUT

Carry-Out1

Logic Elements

Sum

Preliminary

2–11