ADXL180WCPZ-RL Analog Devices Inc, ADXL180WCPZ-RL Datasheet - Page 27

ADXL180WCPZ-RL

Manufacturer Part Number

ADXL180WCPZ-RL

Description

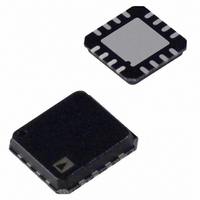

IC ACCELEROMETER CONFIG 16-LFCSP

Manufacturer

Analog Devices Inc

Series

iMEMS®r

Datasheet

1.ADXL180WCPZ-RL.pdf

(60 pages)

Specifications of ADXL180WCPZ-RL

Axis

X or Y

Acceleration Range

±50g, 100g, 150g, 200g, 250g, 350g, 500g

Voltage - Supply

5 V ~ 14.5 V

Output Type

Analog

Bandwidth

100Hz ~ 800Hz Selectable

Mounting Type

Surface Mount

Package / Case

16-LFQFN, CSP Exposed Pad

Package Type

LFCSP EP

Operating Supply Voltage (min)

5V

Operating Temperature (min)

-40C

Operating Temperature (max)

125C

Operating Temperature Classification

Automotive

Product Depth (mm)

5mm

Product Height (mm)

1.43mm

Product Length (mm)

5mm

Mounting

Surface Mount

Pin Count

16

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Sensitivity

-

Interface

-

Lead Free Status / Rohs Status

Compliant

Other names

ADXL180WCPZ-RLCT

TRANSMISSION ERROR DETECTION OPTIONS

There are two error checking methods available: a 3-bit CRC

and a 1-bit parity check. These are determined by the user-

selected Bit ERC.

Table 20. Error Check (ERC) Bit Options

ERC

0

1

CRC Encoding

The ADXL180 can be programmed to utilize a 3-bit CRC. The

polynomial used for the encoding is x

Definition

A 3-bit CRC is included in the message. CRC is calculated

using the polynomial x

One parity bit is included in the message. CRC is not used.

It is a bit that is set such that even parity is achieved in

the transmitted message.

3

+ x

1

+ x

3

0

. (Default.)

+ x

1

+ x

0

. The CRC

Rev. A | Page 27 of 60

calculation is performed from MSB to LSB on the entire data

frame. The CRC state registers are initialized to zero. Therefore,

when checking the result of the transmission, the final CRC

check state should be zero. The three CRC bits are always the

three least significant bits in the transmission.

Parity Encoding

The ADXL180 can be programmed so that the LSB of each data

transmission contains a 1-bit parity check bit. The 1-bit parity

check is even parity. The parity algorithm sets the parity bit to

be either a one or a zero; thus, the resulting number of ones

transmitted in the data frame is always an even number.

ADXL180